|

Добрый день можно поинтересоваться где брать литературу предложенную в курсе ?Большинство книг я не могу найти в известных источниках |

Модели цифровых устройств

Монтажная логика

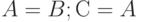

Логическое моделирование выполняется при предположении, что информация обрабатывается логическими элементами и передается в схеме другим элементам в одном направлении (от входов к выходам в самом элементе, от выходов элемента к входам других элементов в схеме). Но эти предположения не всегда выполняются. Например, достаточно часто при некоторых технологиях используется "монтажная логика". При этом выходы логических элементов соединяются непосредственно и в месте соединения реализуется логическая функция  (или

(или  в зависимости от используемой технологии и мощности соединяемых элементов). Такой элемент называется "проводным (монтажным)

в зависимости от используемой технологии и мощности соединяемых элементов). Такой элемент называется "проводным (монтажным)  ". Для того чтобы подобные ситуации могли обрабатываться в процессе логического моделирования в схему вводится дополнительный фиктивный логический элемент

". Для того чтобы подобные ситуации могли обрабатываться в процессе логического моделирования в схему вводится дополнительный фиктивный логический элемент  , как это показано на рис.2.12 . Здесь на рис.2.12 а) представлена исходная схема, а рис.2.12 б) – преобразованная схема с фиктивным элементом. Следует отметить, что логическое значение на выходе фиктивного элемента при этом всегда правильное, но значения на его входах при такой модели не всегда соответствует реальной схеме. В этой модели входы фиктивного элемента могут иметь различные значения (например,

, как это показано на рис.2.12 . Здесь на рис.2.12 а) представлена исходная схема, а рис.2.12 б) – преобразованная схема с фиктивным элементом. Следует отметить, что логическое значение на выходе фиктивного элемента при этом всегда правильное, но значения на его входах при такой модели не всегда соответствует реальной схеме. В этой модели входы фиктивного элемента могут иметь различные значения (например,  для схемы

рис.

2.12б), хотя очевидно, что в реальной схеме они принимают одинаковое значение. При корректном моделировании после вычисления значения выхода фиктивного элемента С его надо присвоить также и обоим входам

для схемы

рис.

2.12б), хотя очевидно, что в реальной схеме они принимают одинаковое значение. При корректном моделировании после вычисления значения выхода фиктивного элемента С его надо присвоить также и обоим входам  . На

рис.

2.12б) это показано пунктирными стрелками. Следует отметить, что введение подобных фиктивных элементов нарушает соответствие между моделью и реальной схемой, что может, например, привести к ошибочной интерпретации результатов моделирования неисправной схемы или построения тестов. Более корректно такие ситуации (и многие другие) моделируются на уровне электрических схем.

. На

рис.

2.12б) это показано пунктирными стрелками. Следует отметить, что введение подобных фиктивных элементов нарушает соответствие между моделью и реальной схемой, что может, например, привести к ошибочной интерпретации результатов моделирования неисправной схемы или построения тестов. Более корректно такие ситуации (и многие другие) моделируются на уровне электрических схем.

Модели уровня ЯРП

В настоящее время для описания функционирования дискретных устройств широко используются специализированные языки описания цифровой аппаратуры – HDL, которые стали стандартным инструментом при проектировании ДУ [ 2.7 ] . Сейчас вопрос стоит не в том - использовать или не использовать эти языки, а какой именно язык следует использовать при проектировании данного ДУ. Современные языки позволяют описывать ДУ на структурном (вентильном) и функциональном (поведенческом) уровне. В настоящее время они больше используются для описания ДУ на функциональном или уровне регистровых передач. Использование таких языков позволяет существенно сократить срок проектирования и повысить размерность проектируемых ДУ. Следует отметить, что в настоящее время часто срок жизни (эксплуатации) цифровых систем меньше срока его проектирования. В настоящее время наиболее популярными являются языки проектирования SpecC, VHDL (Very high speed integrated circuits HDL) и Verilog HDL.

Рассмотрим основные конструкции этих языков. В них входы, выходы, внутренние состояния и регистры ДУ представляются соответствующими переменными. Как правило, эти переменные должны быть объявлены в начале описания устройства. Например, порты описываются следующим образом:

Два регистра могут быть описаны следующим образом:

![REGISTER R1[1->32], R2[16] ,](/sites/default/files/tex_cache/df31b0dca465fdd4d386c2b7ffc2a416.png)

где в квадратных скобках указана их разрядность. Аналогичные описания существуют и для других типов устройств (переменных). Так память из 32-разрядных 256 элементов описывается с помощью объявления

![MEMORY[1->256:32]](/sites/default/files/tex_cache/2b46bf8ddfe9212d0fa4a3d1a8d16b22.png)

Обработка и пересылка может быть описана следующим образом:

где выполняется сложение содержимого двух регистров  и

и  и пересылка результата в регистр

и пересылка результата в регистр  .

.

Для описания функционирования ДУ обычно используется следующие группы операторов ЯРП.

- Логические операторы:

. Эти операторы обычно выполняются над регистрами или некоторыми их разрядами.

. Эти операторы обычно выполняются над регистрами или некоторыми их разрядами. - Операторы сравнения: больше (>), меньше (<), больше или равно (

), меньше или равно(

), меньше или равно( ), равно (

), равно ( ), не равно (

), не равно ( ). Эти операторы выполняются над векторами или скалярными переменными. Результатом является логическое значение

). Эти операторы выполняются над векторами или скалярными переменными. Результатом является логическое значение  или

или  .

. - Арифметические операторы: сложение (

), вычитание (

), вычитание ( ), умножение (

), умножение ( ), деление (

), деление ( ), инкремент, декремент (используются, в основном, для моделирования функционирования счетчиков ).

), инкремент, декремент (используются, в основном, для моделирования функционирования счетчиков ). -

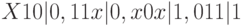

Битовые операции: правый сдвиг (

), левый сдвиг (

), левый сдвиг ( ), циклический правый сдвиг (

), циклический правый сдвиг ( ), циклический левый сдвиг (

), циклический левый сдвиг ( ) и конкатенация (сцепление). Эти операторы выполняются над векторными переменными.

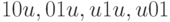

) и конкатенация (сцепление). Эти операторы выполняются над векторными переменными. - Операция пересылки

содержимого регистра

содержимого регистра  в регистр

в регистр  . Эта операция может быть унарной (выполняется над одним операндом, например,

. Эта операция может быть унарной (выполняется над одним операндом, например,  ), или бинарной (выполняется над двумя операндами, например,

), или бинарной (выполняется над двумя операндами, например,  ). Единичная задержка неявно ассоциируется с операцией пересылки. Произвольная задержка должна быть указана явно (например,

). Единичная задержка неявно ассоциируется с операцией пересылки. Произвольная задержка должна быть указана явно (например,  ).

). - Условные операторы:

- бинарный:

;

;

где

является условием, а

является условием, а  и

и  – блоки, состоящие из операторов.

– блоки, состоящие из операторов. - оператор ветвления типа

:

:

где

являются выражениями и

являются выражениями и  – блоки. Таким образом, может быть описан, например, дешифратор.

– блоки. Таким образом, может быть описан, например, дешифратор.

- бинарный:

Конечные автоматы могут быть описаны двумя способами. При первом (функциональном) подходе языковыми средствами с помощью условных операторов описывается непосредственно таблица переходов и выходов автомата [ 2.7 ] . При втором (структурном) подходе фактически автомат представляется и описывается структурной моделью рис. 2.5.

В соответствии с трактовкой понятия времени ЯРП можно разделить на две категории: процедурные и непроцедурные языки. Процедурные ЯРП похожи на обычные языки программирования (такие как Паскаль, С и т.п.), где операторы и утверждения языка выполняются последовательно таким образом, что результат выполненного оператора становится доступным для следующих операторов. Например, при выполнении операторов  содержимое переменной (регистра)

содержимое переменной (регистра)  станет равным содержимому переменной

станет равным содержимому переменной  . Поэтому некоторые процедурные ЯРП являются расширением обычных языков программирования (например, С, HDL). С другой стороны операторы и утверждения непроцедурных языков выполняются параллельно. В непроцедурных языках выполнение операторов

. Поэтому некоторые процедурные ЯРП являются расширением обычных языков программирования (например, С, HDL). С другой стороны операторы и утверждения непроцедурных языков выполняются параллельно. В непроцедурных языках выполнение операторов  соответствует обмену содержимым регистров

соответствует обмену содержимым регистров  и

и  . Современные языки описания аппаратуры часто являются смешанными, то есть имеют как процедурные так и не процедурные средства описания и интерпретации.

. Современные языки описания аппаратуры часто являются смешанными, то есть имеют как процедурные так и не процедурные средства описания и интерпретации.

Ключевые термины:

Комбинационные схемы – схемы из логичесчких элементов, которые реализуют систему булевых функций и, как правило, не имеют обратных связей.

Последовательтностные схемы – схемы из логичесчких элементов, которые реализуют конечный автомат и, как правило, имеют обратные связи.

Функциональный модели – учитывают только логику функционирования ЦУ и не принимают во внимание внутреннюю организацию устройства.

Структурные модели – описывают внутреннюю организацию устройства в виде логических схем.

Бинарная диаграмма (альтернативный граф) – ациклический ориентированный граф, который представляет булевы функции.

Языки регистровых передач – специализированные языки описания цифровых устройств, примером которых являются:VHDL, VERILОG и т.п.

Краткие итоги

В данной лекции вводятся основные модели ЦУ, которые в дальнейшем используются в курсе лекций.

В разделе 2.1 рассматриваются функциональные модели , которые абстрагируются от внутренней организации устройства и учитывают только логику функционирования. Раздел 2.1.1 описывает функциональные модели комбинационных схем в виде системы булевых функций. В разделе 2.1.2 представлены функциональные модели схем с памятью в виде конечных автоматов. Раздел 2.1.3 посвящен функциональным моделям в виде бинарных диаграмм .

В разделе 2.2 описаны структурные модели в виде логических схем. В разделе 2.2.1 приведен пример внешнего описания схемы на простом специализированном языке. Раздел 2.2.2 посвящен свойствам структурных моделей , включая ранжирование элементов схемы.

Раздел 2.3 посвящен моделям уровня языков регистровых передач , где приведены основные типы операторов ЯРП.

Вопросы и упражнения

- Чем отличаются комбинационные устройства от последовательностных?

- Чем отличаются функциональные модели от структурных ?

- Приведите функциональные модели для комбинационных схем .

- Чем отличаются таблицы истинности от примитивных кубов?

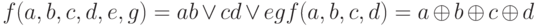

- Могут ли приведенные ниже кубы быть примитивными кубами функции

?

?

- Рассмотрите булеву функцию, определенную примитивными кубами:

-

. Найдите значение этой функции на следующих входных наборах:

. Найдите значение этой функции на следующих входных наборах:  .

. - Приведите функциональные модели для схем с памятью.

- Что такое автомат Мили и как его можно описать?

- Приведите каноническую модель схемы с памятью.

- Чем отличается асинхронный автомат от синхронного?

- Что такое альтернативные графы (бинарные диаграммы) ?

- Постройте альтернативный граф булевой функции из упражнения 5.

- Постройте альтернативный граф для функций:

- Постройте таблицу переходов-выходов синхронного автомата с одним входом и одним выходом, который распознает входную последовательность

.

. - Постройте граф переходов-выходов этого автомата

- Постройте также схему для распознавания таких перекрывающихся последовательностей и дает на входную последовательность

выходную последовательность

выходную последовательность  .

. - Напишите ЯРП модели для D-триггера с передним фронтом переключения.