Опубликован: 17.03.2025 | Доступ: свободный | Студентов: 0 / 0 | Длительность: 07:30:00

Лекция 6:

Арифметико-логическое устройство

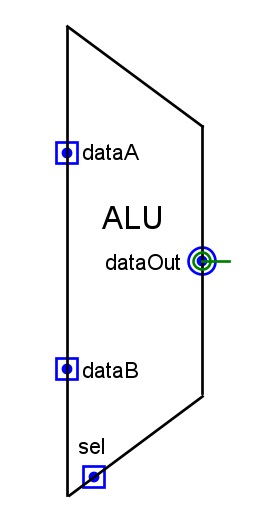

В инструменте редактирования внешнего вида отредактировать условно- графическое обозначение АЛУ, например, как показано на рисунке 6.26.

Для проектирования АЛУ в среде Quartus создать новый каталог с именем CPU. Имя проекта для создаваемого процессора определить RISC_V (с данного момента осуществляется проектирование процессора). В окне Family, Device… выбрать соответствующее семейство и тип микросхемы (если имеется отладочная плата для разработки. Нажать кнопку Finish.

Далее создать новый Verilog HDL File сохранить его под именем ALU.v.

В созданный файл ввести код из листинге 6.6

module ALU( input [31:0] srcA, srcB, input [3:0] aluControl, // вход дешифратора операций АЛУ (рассматривается далее) output reg [31:0] aluResult, output zero ); always @(*) begin case (aluControl) 4'b0000: aluResult = srcA + srcB; // ADD 4'b0001: aluResult = srcA - srcB; // SUB 4'b0010: aluResult = srcA & srcB; // AND 4'b0011: aluResult = srcA | srcB; // OR 4'b0100: aluResult = srcA ^ srcB; // XOR 4'b0101: aluResult = srcA << srcB[4:0]; // SLL 4'b0110: aluResult = srcA >> srcB[4:0]; // SRL 4'b0111: aluResult = $signed(srcA) >>> srcB[4:0]; // SRA 4'b1000: aluResult = (srcA < srcB) ? 32'd1 : 32'd0; // SLT 4'b1001: aluResult = ($signed(srcA) < $signed(srcB)) ? 32'd1 : 32'd0; // SLTU default: aluResult = 32'b0; // по умолчанию endcase end assign zero = (aluResult == 32'b0) ? 1'b1 : 1'b0; endmoduleЛистинг 6.6.

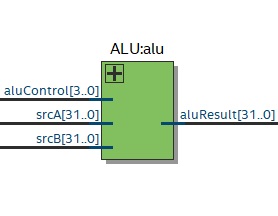

На рисунке 6.27 приведен вид RTL cозданного модуля.

Дать ответы на следующий вопросы:

- Каким образом осуществляется ускорение переноса (проанализировать дополнительные источники);

- Как можно реализовать коммутацию выходных шин с арифметических блоков и логических элементов в АЛУ без применения мультиплексора.

Литература

- Орлов С.А. Цилькер Б.А. Организация ЭВМ и систем: Учебник для ВУЗов. 3-е изд. СПб.2014.-688с.:ил. (С.182-214).

- Угрюмов Е.П. Цифровая схемотехника: учеб. пособие для вузов. - 2-е изд., перераб. и доп. СПб.: БХВ-Петербург, 2007. - 800 с.: ил. (С.129-139).

Дополнительная литература

- С. Харрис, Д. Харрис. Цифровая схемотехника и архитектура компьютера RISC-V/ пер. с англ. В.С. Яценкова, А.Ю. Романова; под. ред. А.Ю. Романова.-М.: ДМК Пресс, 2021. - 810 с.: ил.