Арифметико-логическое устройство

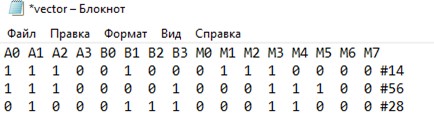

Для проверки корректности схемы можно создать тестовую таблицу работы. Для этого в текстовом редакторе (Блокнот) создать файл. Первой стройкой ввести через пробелы имена входных слов и выходного слова. Второй, третьей и далее строками вводятся тестовые значения. На рисунке 6.20 приведены три строки. В первой вводится два операнда 7 и 2, результат 14. Второй строкой введены операнды 7 и 8, результат 56. В третье строке в результате введена ошибка. Операнды 2 и 14. Результат 28 в двоичном коде выглядит следующим образом 00011100 В строке с ошибкой третьем разряде введен лог. "0 ", соответственно код имеет следующий вид - 00011000. На рисунке приведено содержимое файла тестирования. Знак # применяется как символ комментария.

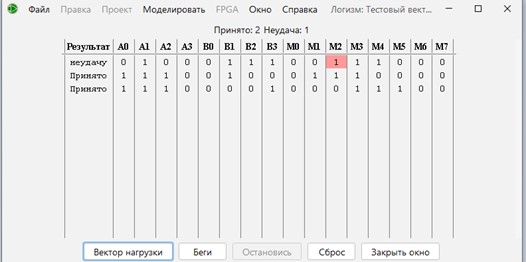

Далее в меню "Моделировать " - "Тестовый вектор ". В открывшемся окне нажать кнопку "Вектор нагрузки ", выбрать файл с тестовым содержимым. Результат работы показан на рисунке 6.21. Разряд в котором содержится ошибка подсвечен красным и выведен результат, который формирует устройство. В столбце "Результат " в строке с ошибкой указывается "неудачу ". Обработанные верно строки подписаны "Принято ".

Данный метод считается тестирование с "белым ящиком ", когда тестировщик знает внутреннее устройство и принцип функционирования устройства.

Самостоятельно:

Составить файл тестовый вектор, содержащий ошибочные тесты и верные решения не менее 10 строк.

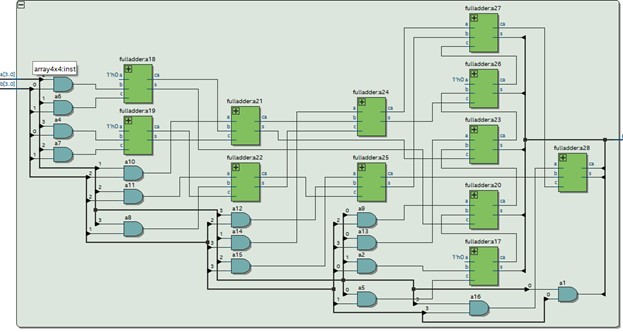

В листинге 6.4 приведен пример реализации методом структурного описания схемы матричного умножителя, показанного на рисунке 6.18 на языке Verilog HDL.

module multiplication4x4(a,b,x); //входы умножителя input [3:0]a,b; //выход output [7:0]x; //внутренняя шина wire [39:0]w; //получение частных and a1(w[0],a[0],b[0]); and a2(w[1],a[1],b[0]); and a3(w[2],a[2],b[0]); and a4(w[3],a[3],b[0]); and a5(w[4],a[0],b[1]); and a6(w[5],a[1],b[1]); and a7(w[6],a[2],b[1]); and a8(w[7],a[3],b[1]); and a9(w[8],a[0],b[2]); and a10(w[9],a[1],b[2]); and a11(w[10],a[2],b[2]); and a12(w[11],a[3],b[2]); and a13(w[12],a[0],b[3]); and a14(w[13],a[1],b[3]); and a15(w[14],a[2],b[3]); and a16(w[15],a[3],b[3]); assign x[0]=w[0]; //коммутация сумматоров с внутренними сигналами частных fulladder a17(1'b0,w[1],w[4],w[16],w[17]); fulladder a18(1'b0,w[2],w[5],w[18],w[19]); fulladder a19(1'b0,w[3],w[6],w[20],w[21]); fulladder a20(w[8],w[17],w[18],w[22],w[23]); fulladder a21(w[9],w[19],w[20],w[24],w[25]); fulladder a22(w[10],w[7],w[21],w[26],w[27]); fulladder a23(w[12],w[23],w[24],w[28],w[29]); fulladder a24(w[13],w[25],w[26],w[30],w[31]); fulladder a25(w[14],w[11],w[27],w[32],w[33]); fulladder a26(1'b0,w[29],w[30],w[34],w[35]); fulladder a27(w[31],w[32],w[35],w[36],w[37]); fulladder a28(w[15],w[33],w[37],w[38],w[39]); //коммутация выходных линий с внутренними assign x[1]=w[16]; assign x[2]=w[22]; assign x[3]=w[28]; assign x[4]=w[34]; assign x[5]=w[36]; assign x[6]=w[38]; assign x[7]=w[39]; endmodule //модуль полного сумматора module fulladder(a,b,c,s,ca); //входы input a,b,c; //outputs output s,ca; //функционал полного сумматора. assign s=(a^b^c); assign ca=((a&b)|(b&c)|(c&a)); endmoduleЛистинг 6.4.

На рисунке 6.22 представлен данный цифровой блок на уровне RTL

В АЛУ применяется узел сравнения входных слов. Данную операцию выполняет комбинационная схема - цифровой компаратор (в среде Logisim данный блок имеется и приведен в таблице 6.3).

Цифровые компараторы обычно делят на:

- компараторы равенства (тождественные) - они имеют один/два выхода, отражающих равнозначность входных слов (сигналов).

- компараторы по величине (схемы сравнения). Реализацию данного узла можно осуществить с применением сумматора и дополнительно включаемых логических элементов.

На рисунке 6.23 приведена функциональная схема сравнения двух бит. При поступлении лог. "1 " на оба входа за счет инверсии на входах элементы D1_1 и D1_2 сформируют на выходах лог. "0 ", тем самым сработает элемент@ ИЛИ -НЕ " D1_3 с сигналом равенства. Аналогично схема сработает при поступлении лог. "0 " на оба входа. Если на входе А будет присутствовать лог "1 ", на входе В лог. "0 ", то активным элементом данной схемы будет D1_2, который сформирует сигнал лог "1 " на выходе Ab (A<B) и наоборот.