Арифметико-логическое устройство

Для составления логической функции для S можно обратиться к логическому конвертеру - функция "Исключающее ИЛИ " (XOR).

При сложении старших разрядов многоразрядных двоичных слов необходимо в схеме учесть перенос из предыдущего (младшего) разряда. Такое устройство является полным сумматором (full adder). Оно должно иметь три входа: А и В - одноименные разряды двух складываемых чисел, Сi - входной перенос из предыдущего (младшего) разряда (англ. carry in - входной перенос) и два выхода: S - сумма в данном разряде и Co - перенос в следующий (старший) разряд.

Таблица истинности для одноразрядного сумматора приведена в таблице 6.2.

| Входные сигналы | Выходные сигналы | |||

|---|---|---|---|---|

| A | B | Ci | S | Co |

| 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

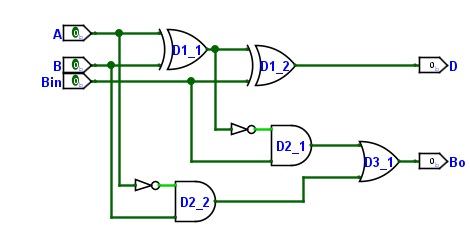

Сумматор удобно представить в виде двух полусумматоров, из которых первый суммирует разряды А и В, а второй к результату прибавляет бит переноса Ci (рисунок 6.4). Цепь D1_1, D1_2 обеспечивает формирование сигнала S. При возникновении лог. "1 " на одном из входов либо при наличии на всех входах лог "1 ". Элемент D2_1 обеспечивает возникновении лог. "1 " на выходе Co элемента "ИЛИ " D3_1(при наличии одного из слагаемых А или В и сигнала переноса из младших разрядов Сin). Элемент D2_2 обрабатывает возникновение переноса, когда на входах А и В присутствуют лог. "1 ".

Приведенная выше схема широко представлена в литературе, но при реализации данного устройства в виде микросхем, схема сумматора значительно отличается.

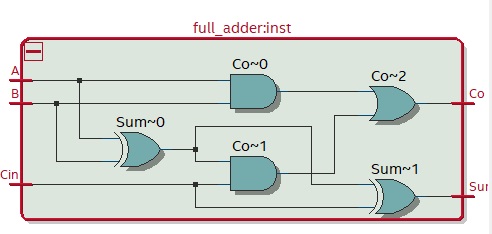

В листинге 6.1 приведен код полного сумматора на языке Verilog HDL. На рисунке 6.5 приведен данный узел на уровне RTL.

module full_adder ( input wire A, // бит операнда А input wire B, // бит операнда В input wire Cin, // вход переноса Cin output wire Sum, // S выход сумма output wire Co // Выход переноса Co ); // получаем сумму assign Sum = A ^ B ^ Cin; // Формирование переноса assign Co = (A & B) | (Cin & (A ^ B)); endmoduleЛистинг 6.1.

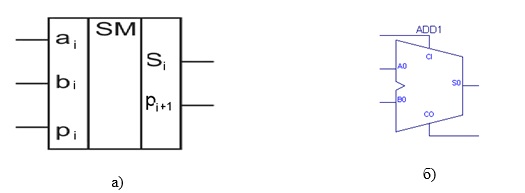

В системе ЕСКД сумматоры изображаются так, как представлено на рисунке 6.6а ( вход Cin может замется на  , выход

, выход  ). На рисунке 6.6б приведено УГО сумматора в системе ANSI. Условное буквенное обозначение сумматоров на схемах - SM.

). На рисунке 6.6б приведено УГО сумматора в системе ANSI. Условное буквенное обозначение сумматоров на схемах - SM.

Обратной схемой сумматора является субтрактор - вычитатель. В двоичнм коде принцип субтрактора, анлогичен работе сумматора. За исключением переноса. В данном случае он занимает из старших разрядов, а выход Bo сигнализирует, что на выходе вычитания получено отрицательное число. По внтуреннему устройству субтрактор схож с сумматором. На рисунке 6.7 приведена блок - схема двооичного вычитателя с последовательным переносом (заем).

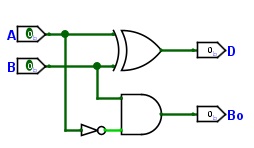

На рискунке 6.8 приведена схема функциональная полувычитателя. На рисунке 6.9 приведена схема функциональная полного вычитателя. Выход разности именуется D (англ. Difference).

Сравнивая схему на рисунке 6.9 со схемой на рисунке 6.4, можно наблюдать отличия только в применении инверторов, которые обеспечивают получение обратного кода. С ним и производится опять же операция сложения. В листинге 6.2 приведен код для субтрактора на языке Verilog HDL. На рисунке 6.10 приведен данный узел на уровне RTL.