Арифметико-логическое устройство

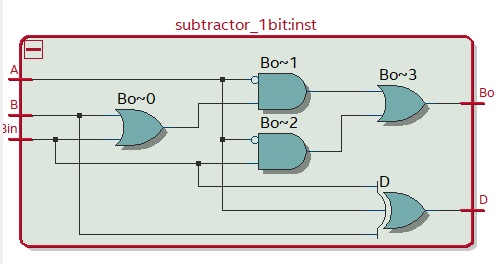

module subtractor_1bit ( input wire A, // Уменьшаемое А input wire B, // Вычитаемое В input wire Bin, // Вход переноса Bin output wire D, // Выход разности output wire Bo // Выход заема ); //Выполнение операции "Исключающее ИЛИ ", аналогично сложению assign D = A ^ B ^ Bin; // Получение сигнала Bo assign Bo = (~A & (B | Bin)) | (Bin & ~A); endmoduleЛистинг 6.2.

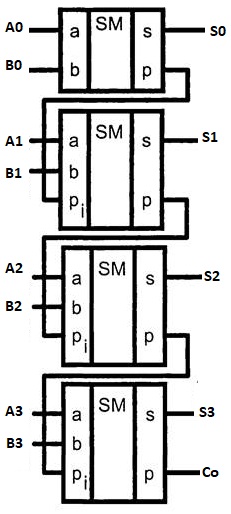

В среде Logisim разрядность сумматора и вычитателя ограничена 64 битами. Для увеличения разрядности обрабатываемых слов применяются различные схемы включения. Для увеличения разрядности сумматоров применяется каскадное включение. Выход переноса Co младшего сумматора подключается к входу Cin старшего сумматора (рисунок 6.11). Каскадное последовательное включение сумматоров снижает быстродействие всей схемы сложения в силу увеличения времени задержки прохождения сигнала переноса из младшего сумматора в старший. Для повышения быстродействия схема с последовательным включением переносов не применяется. Для этого применяются специальные цифровые блоки - схемы ускоренного переноса (СУП), которые описаны в литературе [2].

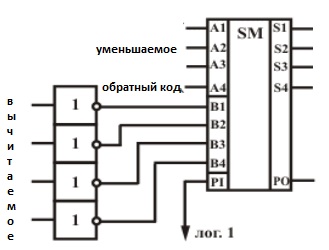

Также для упрощения организации АЛУ возможно отказаться от блока вычитателя, специальным образом организовав коммутацию операнда вычитаемого на сумматоре. Вычитание осуществляется, путем сложения в дополнительных кодах. Для этого вычитаемое, например, операнд В проходит процедуру инверсии - будет получен обратный код числа. На вход Cin будет подан сигнал с уровнем лог. "1 ", обеспечив тем самым дополнительный код. Упрощенная схема организации операции вычитания приведена на рисунке 6.12

Так же в АЛУ выполняется и операция сдвига слов. Хотя существуют сдвиговые регистры, но применение сдвиговых регистров в процессоре в ядре процессора нецелесообразно по следующим причинам:

- необходимо управлять ее ходом (загрузка данных в регистр сдвига, а затем сдвинуть на определенное число разрядов, что потребует организации дополнительной микропрограммы;

- сдвиговые регистры схемотехнически сложнее, чем регистры с параллельной загрузкой данных, усложнение даже нескольких регистров приведет к усложнению всей схемы.

В АЛУ могут осуществляться два вида сдвига: логический влево/вправо

- логический влево/вправо - побитный сдвиг в сторону старших / младших разрядов с заполнением высвобождающихся разрядов;

- арифметический сдвиг вправо при котором сдвинутые вправо биты, отбрасываются, а копии самого левого бита вставляются слева.

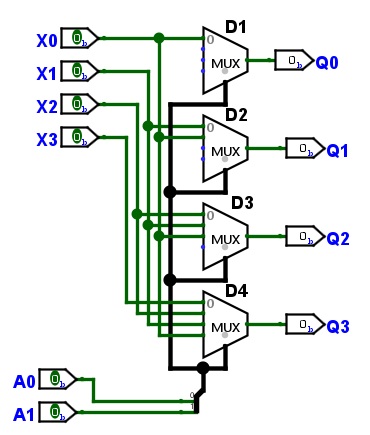

Поэтому для организации операций сдвига в АЛУ применяются мультиплексоры. Рассмотрим организацию сдвига на примере четырехразрядного слова. Для этого будут применятся мультиплексоры, коммутирующие четыре линии (необходимо 4 мультиплексора).

Поэтому для организации данной операции применяются мультиплексоры. Рассмотрим организацию сдвига на примере четырехразрядного слова. Для этого будут применятся мультиплексоры, коммутирующие четыре линии (необходимо 4 мультиплексора).

На рисунке 6.13 приведена функциональная схема устройства логического сдвига. Блок D1 - младший мультиплексор, D4 - старший. Входы сдвигаемого слова Х0-Х4 будут подключены следующим образом. Х0 подключается к входу 0 мультиплексора D1, входу 1 мультиплексора D2, входу 2 мультиплексора D3, входу 3 мультиплексора D4. Вход X1 к 0 входу D2, к 1 входу D3, к входу 2 D4. Вход X2 к 0 входу D3, к 1 входу D4. Вход Х3 к 0 входу D4. За счет такого перекрестного включения линий фактически и организован сдвиг слова.

Адресные входы А0, А1 у всех мультиплексоров объединенны. Этими входы управления определяют сдвиг входного слова. Представленная схема осуществляет сдвиг в сторону старших разрядов (сдвиг влево).

При сдвиге старшие биты будут фактически замещены 0 с неиспользуемых входов (для неиспользуемые входы необходимо подключит к контактам "Земли ", либо константе "0 ". При необходимости сохранения данных из старших разрядов большего слова, неподключенные входы должны будут подключены к старшим разрядам входного сдвигаемого слова. Если же необходимо обеспечить циклический сдвиг слова схему можно видоизменить. Для этого добавить входу управления, назовем его Ci. Далее на схему добавить двухвходовые элементы "И ". Один вход подключить к Ci. Остальные входы подключить к Х1, Х2, Х3 соответственно. Выходы с элементов завести на неиспользуемые входы мультиплексоров. На рисунке 6.14 приведена видоизмененная схема, обеспечивающая циклический сдвиг. Выход D5 подключить к входу 1 D1, входу 2 D2, входу 3 D3. Выход D6 подключить к входу 2 D1, входу 3 D2. Выход D7 подключить к входу 3 D1.