Арифметико-логическое устройство

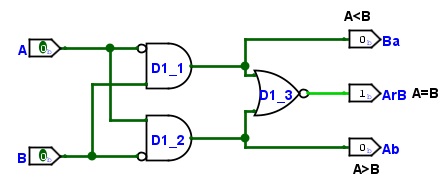

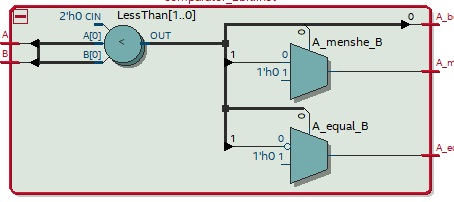

В листинге 6.5 приведен код на языке Verilog HDL, описывающий функциональную схему, приведенную выше. Поведенческое описание схемы выражено через конструкцию if-else и может быть выражено иначе. На рисунке 6.24 приведено RTL представление полученного узла.

module comparator_1bit ( input A, // вход A input B, // вход B output reg A_bolshe_B, // выход A > B output reg A_menshe_B, // выход A < B output reg A_equal_B // выход A == B ); always @ (A or B) begin // установка начального состояния A_ bolshe _B = 0; A_menshe_B = 0; A_equal_B = 0; // Сравнение входов через ветлвение if-else if (A > B) begin A_ bolshe _B = 1; //Если А > B end else if (A < B) begin A_menshe_B = 1; // Если А < B end else begin A_equal_B = 1; // A равно B end end endmoduleЛистинг 6.5.

Самостоятельно

- Реализовать схему сравнения для двух четырехразрядных слов. Для данной схемы реализовать через инструмент "Тестовый вектор " таблицу тестирования. На языке Verilog реализовать аналогичное описание компаратора для данной разрядности слов;

- Реализовать компаратор равенства для двух четырехразрядных слов. На языке Verilog реализовать аналогичное описание компаратора для данной разрядности слов;

Практическая работа 6. "Проектирование АЛУ процессора RISC-V "

При проектировании операционных устройств определяют, выполняемые функции, разрядность и виды входных сигналов, выходные сигналы, сигналы состояний - признаки, например знак, переполнение. Определяют управляющие сигналы и задают их комбинацию для каждой функции - код микрооперации.

Определим для проектируемого устройства операции и зададим коды микроопераций. Формат кодов будет пояснен при разработке блока управления и языка ассемблера RISC-V. В таблице 6.4 приведены виды операций, соответствующие сигналы управления, мнемоника, применяемая в языке ассемблера RISC-V.

| Код операции | Функция | Мнемоника | Вход мультиплексора АЛУ |

|---|---|---|---|

| 0000 | Сложение целых чисел | ADD | 0 |

| 1000 | Вычитание целых чисел | SUB | 8 |

| 0001 | Логический сдвиг влево | SLL | 1 |

| 0010 | Сравнение двух чисел со знаком | SLT | 2 |

| 0011 | Сравнение двух беззнаковых чисел | SLTU | 3 |

| 0101 | Логический сдвиг вправо | SLR | 5 |

| 1101 | Арифметический сдвиг вправо | SRA | 13 |

| 0100 | Логическое "Исключающее ИЛИ " | XOR | 4 |

| 0110 | Логическое "ИЛИ " | OR | 6 |

| 0111 | Логическое "И " | AND | 7 |

Для этого создать каталог RISC в среде Logisim создать новый файл, сохранить его под имением cpu.circ. Далее "Добавить схему ", присвоить название схемы ALU. Разместить на поле следующие блоки из раздела "Арифметика ": сумматор, вычитатель, три сдвигателя, два компаратора. Из раздела элементы: "И ", "Исключающее ИЛИ ", ИЛИ. Из раздела "Плексоры " разместить мультиплексор. У всех элементов свойство "биты данных " задать 32. Мультиплексору в свойство "выбирающие биты " задать 4. Компаратору для операции SLTU в свойстве "Формат числа " выбрать "Беззнаковое ". Для компаратора операции SLT в свойстве "Формат числа " должно быть установлено "Дополнительный код ".

Сдвигателям задать свойство "Тип сдвига ": "Логический левый ", "Логический правый ", "Арифметический правый ".

Так как разрядность операндов 32, соответственно поле управления сдвигом будет иметь разрядность 5 бит. Управление сдвигом будет осуществлять второй операнд. Для изменения разрядности входной шины можно использовать несколько разветвителей и настроить их соответствующим образом (показано выше при построении блока сложения/вычитания - рисунок 6.16). В рассматриваемом примере будут применятся блоки "Расширитель битов ". Данный блок находится в разделе "Проводка ". Для подключения к сдвигателям даннным блокам необходимо задать свойства:

- разрядность входа - 32;

- разрядность выхода - 5;

- тип расширения - 0.

Для преобразования выхода "меньше " у компараторов, который будет включаться в 32-х разрядную шину также необходимо установить расширители битов, задав свойства:

- разрядность входа - 32;

- разрядность выхода - 5;

- тип расширения - 1.

На поле добавить входы и выходы с разрядностью 32.

Для упрощения коммутации шин данных в созданном примере применяются "тоннели ". Для операндов предлагается дать свойства меткам тоннелей OP1, OP2. Выходы элементов также подключить к тоннелям с метками "outМНЕМОНИКА ОПЕРАЦИИ ", например "outADD ". Тоннели с операциями подключить к входам мультиплексора согласно коду операции (четвертый столбец таблицы 6.4 указывает номер входа).

На рисунке приведена схема функциональная спроектированного блока АЛУ.

На рисунке 6.25 приведена схема функциональная спроектированного блока АЛУ.