|

Здравствуйте! Прошел курс, а где экзамен? Как сертификат получить? Без экзамена? |

Последовательностная логика. Регистры

Необходимые материалы для лекции Logisim-04zip и Quartus-04.zip.

Основным составным элементом любого процессора, определяющего его возможности является регистр.

Регистром называется последовательностное устройство, предназначенное для приёма, хранения, сдвига (простых преобразований) данных в двоичном коде. Базовыми элементами регистра являются триггеры, которые дополняются комбинационными логическими элементами для реализации различных связей между триггерами и управления приёмом/ передачей информации. Разрядность регистра определяется количеством триггеров, применяемых для его реализации.

Под простыми преобразованиями понимают сдвиг чисел на заданное количество разрядов, а также преобразования последовательного кода в параллельный или параллельного в последовательный.

Регистры классифицируют:

-

По функциональным свойствам (по виду выполняемых функций):

- накопительные регистры (регистры памяти, хранения);

- сдвигающие регистры (регистры сдвига вправо/ влево);

-

По способу ввода и вывода информации:

- параллельные регистры;

- последовательные регистры;

- комбинированные регистры (параллельно-последовательные, последовательно-параллельные);

- кольцевые регистры (счетчик в кодах Джонсона);

- многофункциональные регистры.

Параллельные регистры

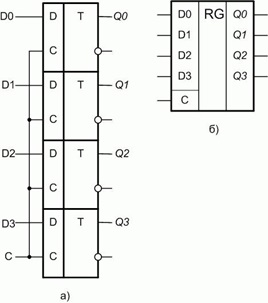

В параллельном регистре на тактируемых D-триггерах код подается на информационные входы всех триггеров и записывается с приходом тактового импульса. В литературе параллельные регистры на D-триггерах называют регистры-защелки. На рисунке 4.1.а приведена функциональная схема простейшего регистра защелки на 4 триггерах (4-х разрядный параллельный регистр). На рисунке 4.1.б приведено его условное графическое обозначение, где D0-D3 - входы данных. С - тактовый вход управления записью в регистр. Q0-Q3 - выходы данных. Условное буквенное обозначение регистров - RG.

Преимуществом приведенного регистра является то, что не требуется предварительная очистка его триггеров. Перевод в состояние логических "1" ли "0" осуществляется за один такт прямым и инверсным сигналом на входе D.

Параллельные регистры обладают следующими свойствами:

- Выходная информация изменяется с подачей нового кода и приходом следующего импульса записи.

- Параллельные регистры могут используются при организации оперативной памяти небольшого объема. Число триггеров в них равно максимальной разрядности хранимых слов.

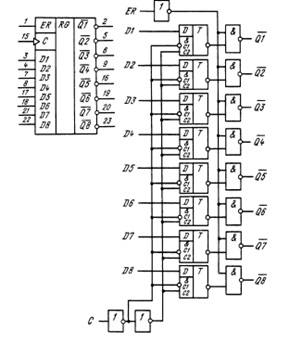

Помимо управления записью в регистр может существовать потребность в управлении выходами регистра. Это может потребоваться при работе нескольких регистров с одной шиной. Исходя из знаний о комбинационной логике можно предположить, что для управления выходом можно использовать логический элемент "И" (AND)/ "И-НЕ". В литературе [1] можно найти схемы с управлением выходом на данном элементе (как показано на рисунке 4.2). Но это категорически неверно.

Проверить данное утверждение можно на практике, реализовав схему регистра, подобного приведенному на рисунке выше в среде Logisim Evolution. Для этого реализуем три четырёхразрядных регистра. Создав новый файл, добавим в него новую схему и назовем ее d_reg. В новой схеме разместим четыре D-триггера вертикально и объединим все тактовые входы (рисунок 4.4.а). Объединенный вход подключим к элементу вход. Метке входа присвоим имя С (рисунок 4.4.б).

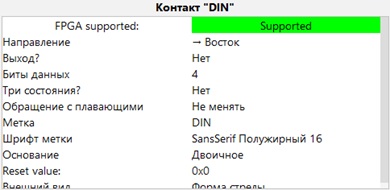

Далее необходимо добавить входы данных. Для проектируемого регистра будет использоваться один многоразрядный вход. В свойстве "Биты данных" элемента вход задается разрядность - 4, свойству метки задается "DIN" (рисунок 4.4).

К входу необходимо подключить элемент шины, который собирает множество сигнальных проводов в единый графический элемент с соответствующей разрядностью. Данный элемент имеет наименование "Разветвитель" и находится в разделе "Проводка". Для входа DIN разветвителю необходимо определить разрядность в свойстве "Разрядность входа" - 4, также задать 4 свойству "Веерный выход". В свойстве "Внешний вид" выбрать "Леворукий", а в свойстве "Направление" - "Восток". Остальные свойства оставить неизменными (рисунок 4.5).