Опубликован: 17.03.2025 | Доступ: свободный | Студентов: 0 / 0 | Длительность: 07:30:00

Лекция 4:

Последовательностная логика. Регистры

| № варианта | Емкость регистрового банка памяти (разрядность порта Х кол-во регистров) |

|---|---|

| 1,7,13,19 | 2х8 |

| 2,8,14,20 | 16х8 |

| 3,9,15,21 | 32х4 |

| 4,10,16,22 | 4x16 |

| 5,11,17,23 | 8x8 |

| 6,12,18,24 | 8x32 |

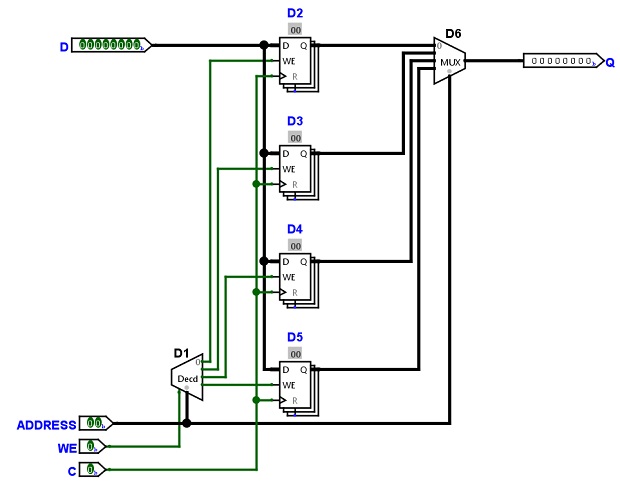

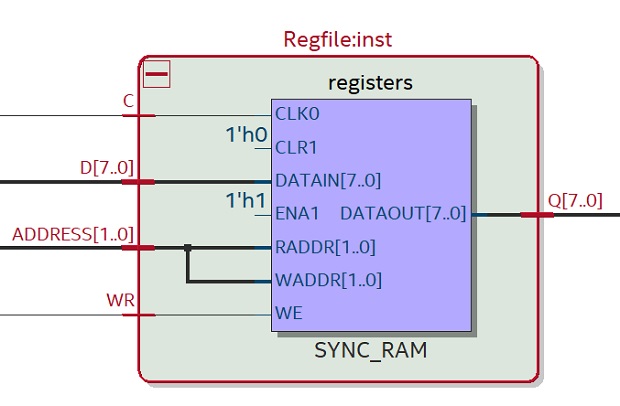

В листинге 4.4 приведен код на языке Verilog HDL, описывающий рассмотренный банк регистровой памяти. На рисунке 4.39 приведен его RTL вид.

module Regfile ( // описываем входы и выходы их параметры

input wire C,

input [1:0] ADDRESS,

input wire [7:0] D,

input wire WE,

output wire [7:0] Q

);

reg [7:0] registers [0:7];// создаем регистры

assign Q = registers[ADDRESS];// подключаем выходы к регистрам

always @(posedge C) begin // в случае фронта по синхровходу

if (WE) begin // если присутсвует разрешение записи

registers[ADDRESS] <= D;//записываем данные с шины данных входа

end

end

endmodule

Листинг

4.4.

В процессорах регистры организовываются в регистровые банки схожим образом, но с более сложными схемотехническими решениями и описанием на языках аппаратуры.

Литература

- Р.В. Данилов. Применение интегральных микросхем в электронной вычислительной технике: Справочник. - М.: Радио и связь, 1986.- 384.: ил.

Дополнительная рекомендуемая литература

- С. Харрис, Д. Харрис. Цифровая схемотехника и архитектура компьютера RISC-V/ пер. с англ. В.С. Яценкова, А.Ю. Романова; под. ред. А.Ю. Романова.-М.: ДМК Пресс, 2021. - 810 с.: ил. (с 116-117, 154-158).

- Микушин А.В. Цифровые устройства и микропроцессоры: учебн. пособине. - СПб.: БХВ-Петербург, 2010 - 832 с.: ил. (С. 144 - 147)

- Романов А.Ю. Цифровой синтез RISC-V. - М.: ДМК Пресс, 2024. - 636с.: ил.