|

Здравствуйте! Прошел курс, а где экзамен? Как сертификат получить? Без экзамена? |

Последовательностная логика. Триггеры

Необходимые материалы для лекции Logisim-03.zip и Verilog-03.zip.

Последовательностное устройство - это цифровое устройство с памятью. Память в данных устройствах обеспечивается за счёт создания положительной обратной связи между элементами. Соответственно выходной сигнал устройства определяется не только текущим состоянии входа, но и рядом предыдущих состояний.

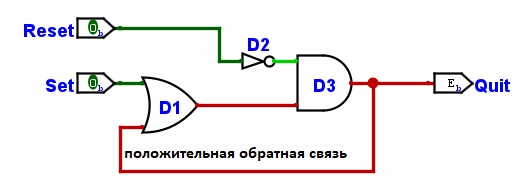

На рисунке 3.1 приведена схема, в которой вводится положительная обратная связь.

На данной схеме вводится два входа. Первый вход будет устанавливать схему в хранение лог. "1". Вход поименован как "Set". Второй вход будет переводить схему в лог. "0" и поименован как "Reset".

Вход "Set" подключен к двухвходовому дизъюнктору D1. Выход с элемента D1 подключен к двухвходовому конъюнктору D3. Сигнал с Reset через инвертор D2 поступает на второй вход элемента D3. Для переключения схемы сигнал "Reset" через инвертор обеспечивает присутствие лог. "1" на втором входе D3.

C выхода D3 снимается сигнал и возвращается на элемент D1, обеспечивая положительную обратную связь.

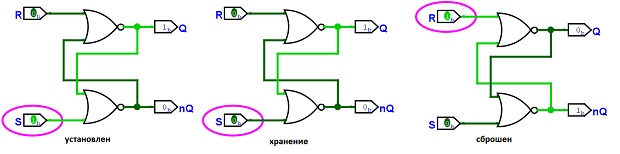

При установке на входе "Reset" лог. "0" и подаче лог. "1" на вход "Set" на выходе "Quit" возникает сигнал лог. "1" (рисунок 3.2а ). Если на входе "Set" установить лог. "0", то схема не изменит своего состояния (рисунок 3.2б ). При смене сигнала на входе "Reset", на выходе "Quit" установится уровень лог. "0" (рисунок 3.2в )

В качестве базовой единицы хранения 1 бита данных применяются триггеры. Триггером называются логическая схема, имеющая два устойчивых состояния, которые называют единичным и нулевым состоянием. Триггер является основным блоком для реализации других более сложных последовательностных устройств.

Базовым триггером является RS (или SR) триггер. Называется он по именам управляющих сигналов, где S - set, R - reset.

Триггеры имеют следующую классификацию:

- по принципу функционирования: RS, D, JK, T;

- по способу записи информации: асинхронные и синхронные;

- по способу функционирования входа управления записью делятся на статические (управляются уровнем) и динамические (управляются изменением сигнала).

- по количеству ступеней обработки данных: одноступенчатые и двухступенчатые.

Триггеры строятся на инверсной логике.

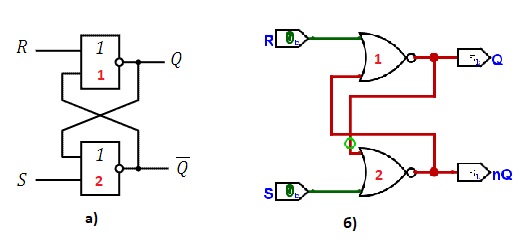

На рисунке 3.3 приведена схема RS-триггера на элементах ИЛИ-НЕ по стандарту ЕСКД (рисунок 3.3а ) и на логических элементах в среде Logisim Evolution (рисунок 3.3б ).

Триггер имеет два входа R и S, а также два выхода Quit (Q) прямой и инверсный Quit (nQ).

Инверсные элементы 2ИЛИ-НЕ соединены кольцом, то есть с выхода одного элемента, сигнал поступает на вход другого. Пока на обоих управляющих входах R и S уровни сигнала неактивные, в данном случае лог. "0", триггер находится в каком-либо одном из двух устойчивых состояний. Если значение сигнала на выходе Q равно лог. "1", то как видно из схемы, этот сигнал, поступая по цепи обратной связи на вход элемента, обозначенного цифрой 2, вызывает появление на выходе инверсного Q (nQ) сигнала с уровнем лог. "0". В свою очередь лог. "0" с выхода инверсного Q (nQ), поступая на вход элемента 1, поддерживает состояние лог "1" на выходе Q. Иначе говоря, при входных сигналах R и S равных нулю, триггер примет одно устойчивое состояние, и будет находится в нем сколь угодно долго. Когда на прямом выходе Q сигнал равен лог "1", то считается что триггер находится в состоянии 1 или установлен.

В силу симметрии схемы она будет столь устойчивой в своём противоположном нулевом состоянии. Когда уровень на выходе Q равен нулю, а уровень на Q инверсном (nQ) соответствует лог. "1", в этом случае считается, что триггер сброшен или погашен. Когда оба управляющих сигнала R и S не активны, то такой режим называют режимом хранения.

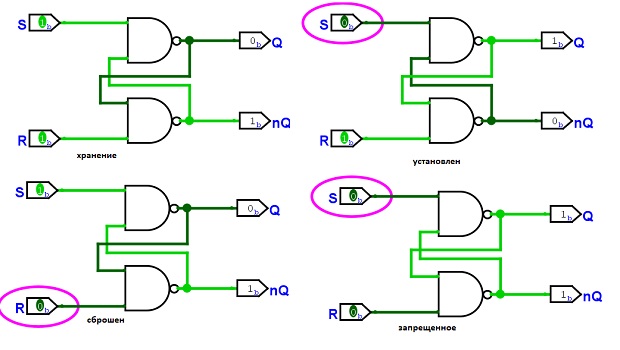

На рисунке 3.4 приведены режимы работы RS триггера. В таблице 3.1 приведена таблица истинности для данного триггера, где Qt - начальное состояние триггера, Q(t+1) - изменяемое состояние.

| R | S | Q(t) | Q(t+1) | Пояснения |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | Режим хранения |

| 0 | 0 | 1 | 1 | |

| 0 | 1 | 1 | 1 | Режим установки |

| 0 | 1 | 1 | 1 | |

| 1 | 0 | 0 | 0 | Режим сброса |

| 1 | 0 | 1 | 0 | |

| 1 | 1 | 0 | X | Запрещенное состояние |

| 1 | 1 | 1 | X |

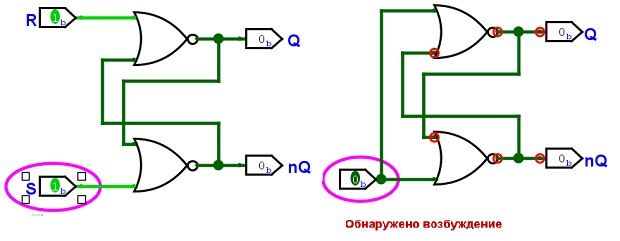

Из таблицы 3.1 видно, что существует запрещенное состояние. Данное состояние необходимо прояснить.

Если на входы RS триггера подать одновременно входной сигнал лог. "1", то на обоих выходах Q и инверсном Q устанавливается лог. "0". Если одновременно снять единицы со входов RS, то элементы триггера начнут переключаться в единичное состояние, каждый стремясь при этом оставить своего партнера в нуле. Какой элемент сработает зависит от коэффициента усиления, скоростей переходных процессов и ряда других неизвестных заранее факторов. Для разработчика схемы результирующее состояние триггера оказывается неопределённым, поэтому комбинация R=S=1 считается запрещённой и в обычных условиях её необходимо блокировать. На рисунке 3.5 показан режим запрещенного состояния (для имитации возврата из запрещённого состояния оставлен один вход).

По отношению к рассмотренному RS триггеру имеется обратный вариант реализации на элементах 2И-НЕ. Такие триггеры управляются сигналами лог. "0". На рисунке 3.6 приведены режимы работы триггера на элементах 2И-НЕ. В таблице 3.2 приведена таблица истинности для данного триггера.