|

Здравствуйте! Прошел курс, а где экзамен? Как сертификат получить? Без экзамена? |

Последовательностная логика. Счетчики

Необходимые материалы для лекции Logisim-05.zip и Quartus-05.zip.

Счетчик - цифровое устройство, предназначенное для подсчета числа сигналов, поступающих на его вход, и фиксации (хранении) этого числа в виде двоичного кода. Счетчики применяются для построения измерительных устройств, таймеров, в устройствах управления частотой, например, делителях частоты. Также счетчики применяются при проектировании схем конечных цифровых автоматов и проектировании блоков управления.

Счетчики строятся на триггерах.

Количество разрядов определяется наибольшим числом, которое должно быть получено в каждом конкретном случае.

В общем случае счетчик имеет  состояний, М - модуль счета, где N - число триггеров, входящих в счетчик.

состояний, М - модуль счета, где N - число триггеров, входящих в счетчик.

Модулем счета является число импульсов, поступивших на счетных вход счетчика, при котором он возвращается в начальное состояние.

Для построения счетчика триггеры включаются в режим работы счетного Т-триггера.

Самым простым проявлением счетчика является делитель частоты на 2.

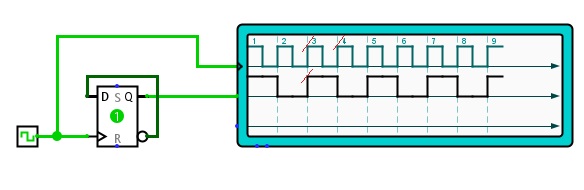

Рассмотрим его на примере D-триггера, включенного в режим Т-триггера. На рисунке 5.1 приведена схема организации делителя входной частоты на 2 (в примере показана входная частота равная 2 Гц). Выход Q с триггера подключен к осциллографу, инверсный выход Q подключен к входу D. Проанализируем фронт третьего синхроимпульса. По фронту триггер переходит в состояние логической &1&, а по фронту синхроимпульса 4 сбрасывается в состояние логического &0&, тем самым на переключение состояния выхода затрачивается два входных такта.

Счетчики классифицируют:

-

По направлению счета:

- инкрементирующие (суммирующие);

- декрементирующие (вычитающие);

- реверсивные.

-

По способу организации цепей переноса:

- последовательный перенос;

- групповой перенос.

-

По способу организации счета:

- асинхронные;

- синхронные.

Асинхронные счетчики строятся из цепочки триггеров, в которых синхросигнал поступает на счетный вход младшего триггера. Выходной сигнал (с прямого или инверсного выхода Q) младшего триггера поступает на счетный вход следующего (старшего) триггера. В данных счетчиках общая задержка прохождения сигнала определяется количеством триггеров. Для данных счетчиков имеются требования по длине импульсов, чтобы обеспечить качественное срабатывание.

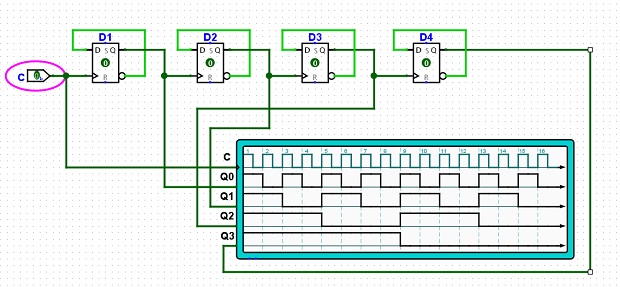

От вариантов включения переносов (с прямого или с инверсного выхода триггера снимается сигнал), а также от вида срабатывания входа синхронизации (передний фронт или задний фронт, по спаду) зависит будет ли счетчик суммирующим или вычитающим. На рисунке 5.2 приведено моделирование работы схемы функциональной вычитающего асинхронного счетчика с последовательным (непосредственным переносом). Модуль счета 16. Из рисунка видно, что с приходом 16 импульса счетчик возвращается в начальное состояние.

В таблице 5.1 приведена таблица переключений счетчика при поступлении на его вход импульсов.

| Номер импульса | Q3 | Q2 | Q1 | Q0 | Состояние счетчика |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | |

| 1 | 1 | 1 | 1 | 1 | 15 |

| 2 | 1 | 1 | 1 | 0 | 14 |

| 3 | 1 | 1 | 0 | 1 | 13 |

| 4 | 1 | 1 | 0 | 0 | 12 |

| 5 | 1 | 0 | 1 | 1 | 11 |

| 6 | 1 | 0 | 1 | 0 | 10 |

| 7 | 1 | 0 | 0 | 1 | 9 |

| 8 | 1 | 0 | 0 | 0 | 8 |

| 9 | 0 | 1 | 1 | 1 | 7 |

| 10 | 0 | 1 | 1 | 0 | 6 |

| 11 | 0 | 1 | 0 | 1 | 5 |

| 12 | 0 | 1 | 0 | 0 | 4 |

| 13 | 0 | 0 | 1 | 1 | 3 |

| 14 | 0 | 0 | 1 | 0 | 2 |

| 15 | 0 | 0 | 0 | 1 | 1 |

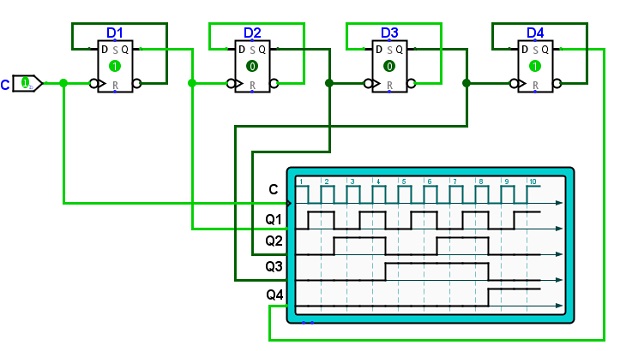

Изменим у триггеров D1-D4 свойство &Срабатывание & с &Передний фронт &, на &Задний фронт & и пронаблюдаем изменения в его работе. Теперь счетчик является суммирующим асинхронным счетчиком с последовательным переносом (рисунок 5.3). В таблице 5.2 приведена таблица переключений. Из рисунка видно, что по спаду 16 импульса счетчик возвращается в начальное состояние.

| Номер импульса | Q3 | Q2 | Q1 | Q0 | Состояние счетчика |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 1 |

| 2 | 0 | 0 | 1 | 0 | 2 |

| 3 | 0 | 0 | 1 | 1 | 3 |

| 4 | 0 | 1 | 0 | 0 | 4 |

| 5 | 0 | 1 | 0 | 1 | 5 |

| 6 | 0 | 1 | 1 | 0 | 6 |

| 7 | 0 | 1 | 1 | 1 | 7 |

| 8 | 1 | 0 | 0 | 0 | 8 |

| 9 | 1 | 0 | 0 | 1 | 9 |

| 10 | 1 | 0 | 1 | 0 | 10 |

| 11 | 1 | 0 | 1 | 0 | 11 |

| 12 | 1 | 1 | 0 | 0 | 12 |

| 13 | 1 | 1 | 0 | 1 | 13 |

| 14 | 1 | 1 | 1 | 0 | 14 |

| 15 | 1 | 1 | 1 | 1 | 15 |

В листинге 5.1 приведен код на языке Verilog HDL, описывающий суммирующий счетчик (в код добавлен вход сброса). В листинге 5.2 приводится листинг файла тестирования. На рисунке 5.4 приводится результат симуляции, который можно сравнить с симуляцией счетчика приведенной на рисунке 5.3. Как видно по диаграммам результат симуляции одинаков.