Опубликован: 17.03.2025 | Доступ: свободный | Студентов: 0 / 0 | Длительность: 07:30:00

Лекция 5:

Последовательностная логика. Счетчики

Самостоятельно

- Добавить выходы к линиям О и CLK передающего или приемного устройства, также добавить восьмиразрядный выход данных присвоить ему имя DATA_OUT.

-

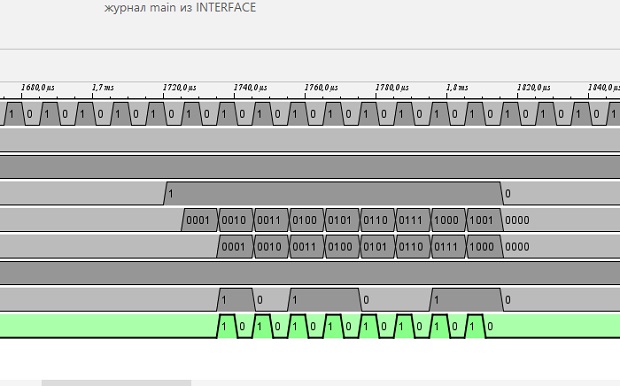

Использовать инструмент &Хроннограмма & (меню &Моделировать & - &Запись в журнал &) получить временную диаграмму работы устройства как показано в примере на рисунке 5.15.

- Рассмотреть варианты добавления третьего управляющего сигнала для включения работы приемного устройства.

- Рассмотреть вариант упрощения избыточности комбинационной схемы передатчика и приемника.

Практическая работа 5. "Проектирование синхронного реверсивного счетчика с параллельной загрузкой"

-

Согласно варианта спроектировать эквивалентную схему счетчика Logisim Evolution с разрядностью равной 4 на заданных триггерах и заданном модуле счета (М).

- Используя инструмент &Хронограмма & оформить временную диаграмму.

- В среде Quartus на языке Verilog HDL создать описание для счетчика среды Logisim согласно таблицы 5.4 истинности. Разработать файл тестирования и выполнить симуляцию.

Дать ответы на следующие вопросы?

- В чем отличие синхронного счетчика от асинхронного?

- Что такое модуль счета счетчика?

- Чему равен модуль счета (N) четырех и пятиразрядного счетчика импульсов?

- На какие входы и какие уровни логического сигнала необходимо подать, чтобы установить счетчик в нулевое состояние и в состояние N - 1?

- Имеют ли асинхронные входы, приоритет над синхронными?

- Какой выходной код установится на выходах трех, четырех и пятиразрядных асинхронных суммирующих счетчиков после подачи на их счетные входы 16, 18, 20, 30 импульсов?