|

Здравствуйте! Прошел курс, а где экзамен? Как сертификат получить? Без экзамена? |

Архитектура процессоров

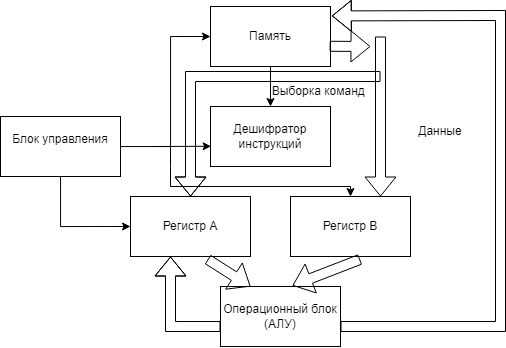

Процессор или центральный процессор - основное устройство любой электронно-вычислительной машины (ЭВМ) в широком понимании данного термина. Он осуществляет управление всеми элементами данной машины и выполняет основной набор вычислительных функций для конкретного решения. Упрощенный вариант процессора приведен на рисунке 7.1.

Блок управления осуществляет выборку инструкции из памяти ЭВМ, дает команды внутри процессора и управляет работой внешних устройств в том числе и памятью. Выбранная инструкция, если содержит данные в памяти, должна через дешифратор инструкций загрузить данные в соответствующие регистры процессора (условные регистр А и В). Дешифратор инструкций, если подразумевается какая-либо операция над данными, активирует соответствующий узел операционного блока. Результат инструкции может быть возвращен в память либо в один из регистров. Далее осуществляется выборка следующей инструкции или переход к другому участку памяти, в случае вызова перехода в результате исполнения инструкции.

Архитектуру процессоров как широкого понятия можно определить набором правил, характеристик, определяющих структуру и функционирование данных устройств.

Первый вид классификации процессоров - система команд процессора (ISA - Instruction Set Architecture). ISA - набор инструкций, которые процессор может выполнять. Инструкции включает в себя как основные команды, так и формат данных, управление памятью и регистры. ISA является ключевым понятием в архитектуре микропроцессорных систем, так как определяет, каким образом программное обеспечение взаимодействует с аппаратным.

Выделяют три категории в данной классификации:

-

CISC (Complex Instruction Set Computer) сложный набор инструкций.

Такие процессоры могут иметь инструкции произвольной длины. Процессоры этой архитектуры способны выполнять несколько операций за несколько тактов. В архитектуре CISC обеспечивается большое количество методов адресации. В тоже время требуется условно небольшое количество регистров необходимых для реализации программы.

К данной категории процессоров относятся x86 совместимые процессоры.

-

RISC (Reduced Instruction Set Computer) упрощенный набор инструкций.

Процессоры RISC имеют одинаковый формат команд. Все команды имеют одинаковую длину. Инструкции исполняются за один такт за исключением сложных арифметических инструкций. RISC процессоры имеют небольшое количество команд по сравнению с CISC. Для повышения быстродействия имеют большое количество неименованных регистров, объединяемых в регистровый файл.

Для RISC процессоров признаками являются:

- расширенный набор регистров;

- симметричность использования определенных регистров;

- упрощенный дешифратор команд за счет простоты организации инструкций;

- простые механизмы адресации данных.

К данной категории процессоров относятся процессоры ARM, различные микроархитектуры микроконтроллеров, например, AVR, PIC, а также решения RISC-V.

-

VLIW (Very Long Instruction Word) - очень длинная машинная команда - архитектура процессоров, характеризующаяся возможностью объединения нескольких простых команд в так называемую связку. Входящие в нее команды должны быть независимы друг от друга и выполняться параллельно. Таким образом, из нескольких независимых машинных команд транслятор формирует одно очень длинное командное слово. Данная архитектура подразумевает, что длинная команда распараллеливается на несколько ядер, исполняющих каждое свою часть. При применении процессоров данной архитектуры большая часть работы выполняется компилятором языка программирования.

К данной категории процессоров относятся процессоры Эльбрус и некоторые решения IA64.

Вторым видом классификации архитектур процессоров является способ доступа к памяти. В данной классификации выделяют две категории:

1.Архитектура Фон Неймана:

- данные и инструкции хранятся в одной памяти;

- инструкции исполняются в строгом порядке, переходы должны быть регламентированы;

- обмен данными между памятью и периферийными устройствами осуществляется под управлением процессора и дополнительными арбитрами.

Данная архитектура имеет следующие преимущества:

- простота организации - использование одного интерфейса для доступа к памяти;

- универсальность работы с памятью.

Недостатки:

- переполнение буфера - ввод данных в ходе исполнения программы может повредить данные или код, размещенные за пределами отведенного сегмента памяти;

- низкая производительность. Данный недостаток вызван тем, что необходимо поочередно выбирать инструкции, а затем выбирать данные из памяти.

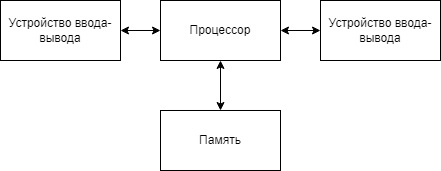

На рисунке 7.2 приведена упрощенная схема организации данной архитектуры.

Архитектура фон Неймана применяется x86 совместимыми процессорами и их последующими поколениями.

Гарвардская архитектура имеет следующие свойства:

- данные и инструкции хранятся раздельно в разных модулях памяти;

- высокое быстродействие за счет параллельного доступа к инструкциям и данным.

Свойства данной архитектуры исключают недостатки архитектуры фон Неймана. Недостатком данной архитектуры является увеличенное количество линий связи с памятью и схемотехническая сложность интерфейса модулей памяти.

Процессоры с RISC системой команд строят по гарвардской архитектуре, для обеспечения максимальной производительности. На рисунке 7.3 приведена упрощенная схема организации гарвардской архитектуры.