Архитектура процессоров

Архитектура и микроархитектура RISC-V

Архитектура RISC-V представляет собой расширяемую открытую свободную систему команд, а также свободно распространяемую микроархитектуру ядра.

Свобода распространения и внесение изменений привлекли пристальное внимание со стороны как энтузиастов в академической среде, так и крупных разработчиков, производителей электроники. На сегодняшний день сформировался пул организаций, поддерживающих и развивающих данную архитектуру. В Российской Федерации также существует команда разработчиков и производителей, объединённая в "Альянс RISC-V ".

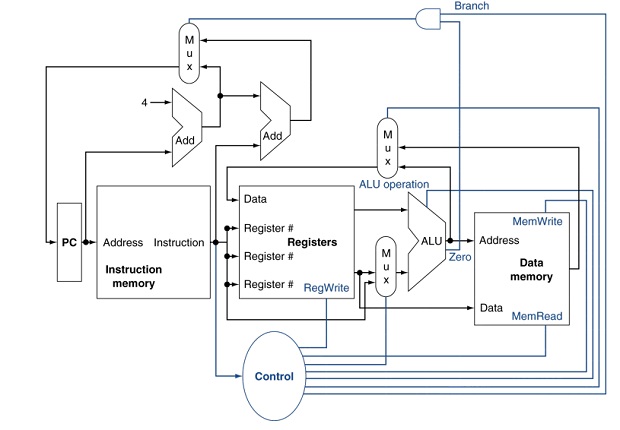

На рисунке 7.8 представлена структурная схема микроархитектуры ядра процессора RISC-V для стандартных целочисленных операций.

На рисунке структурной схемы выделены следующие блоки:

-

PC (program counter) - счетчик адреса памяти инструкции (Instruction memory, IMEM), указывающий на выбираемую из памяти инструкцию. В ряде источников данный счетчик обычно называется указателем команд (IP) или регистром адреса команд (IAR).

После выполнения инструкции значение PC обновляется так, чтобы указывать на следующую инструкцию в последовательности. Вне зависимости от того какая инструкция выполняется, процессор последовательно считывает инструкции, увеличивая счетчик на размер инструкций (4 байта для стандартных 32-х битных инструкций). Данная операция выполняется блоком сумматора текущего адреса и константы 4.

Если в программе есть ветвления, такие как условные операции (например, beq - branch if equal), значение PC будет изменяться не на постоянной основе, а в зависимости от результата операции. На рисунке данный блок обозначен как Branch.

- Instruction memory (IMEM) - память инструкций, хранящая в себе машинный код исполняемой программы. Разрядность шины данных - 32 бита.

- Data memory (DMEM) - память данных. В архитектуре RISC-V играет ключевую роль хранения и управления данными, которые процессор обрабатывает во время выполнения программ. Data Memory используется для хранения переменных, массивов, структур и других видов данных. Процессор может выполнять операции чтения (load) и записи (store) данных. Эти операции позволяют загружать данные из памяти в регистры процессора и сохранять результат вычислений обратно в память.

- Registers - регистровый файл. RISC-V содержит 32 регистра общего назначения. Все операции с ними производятся одинаково, за исключением нулевого (zero) регистра. Попытки записи в данный регистр игнорируются, а чтение всегда возвращает 0. Данная опция полезна, когда не требуется сохранять результат некоторых операций или есть необходимость иметь 0 в качестве операнда.

Несмотря на то, что регистры общего назначения могут использоваться без каких-либо ограничений, некоторые из них, согласно разработанному application binary interface RISC-V, имеют второе имя или алиас, по которому на них могут ссылаться в программном коде.

В таблице 7.1 приводится соответствие номера регистра, его алиас (псевдоним) и назначение.

| Номер регистра | Псевдоним | Назначение |

|---|---|---|

| x0 | Zero | Константа нуля |

| x1 | Ra | Адрес возврата функции |

| x2 | Sp | Указатель стека |

| x3 | Gp | Глобальный указатель |

| x4 | Tp | Локальный указатель данных на уровне потока |

| x5-x7 | t0-t2 | Временные переменные |

| x8 | s0/fp | Указатель кадра для данных локального стека |

| x9 | s1 | Сохраняемая переменная |

| x10-x11 | a0-a1 | Возвращаемые аргументы функций |

| x12-x17 | a2-a7 | Передаваемые в функции аргументы |

| x18-x27 | s2-s11 | Сохраняемые переменные |

| x28-x31 | t3-t6 | Временные переменные |

Сохраняемые переменные (регистры) должны содержать неизменное значение до начала и по окончании вызываемой функции. Временные регистры могут изменять свои значения.

- ALU (arithmetic logic unit) - арифметико-логическое устройство. АЛУ выполняет арифметические, логические операции, операции сравнения и сдвига. В АЛУ базового набора инструкций RV32I выполняется всего 10 операций (для выполнения данных инструкций в предыдущем разделе был спроектирован блок АЛУ в рамках практической работы).

- Control (control unit) - блок управления. В данном случае в него включен и дешифратор инструкций (в разных источниках может отображаться отдельно сразу за IMEM). Блок управления декодирует инструкцию, поступающую из памяти инструкции, и коммутирует соответствующие блоки процессора посредством формирования управляющих сигналов записи/чтения (управления мультиплексорами). Помимо этого, блок анализирует результаты операций и управляет цепями ветвлений. Также этот блок координирует работу выполнения инструкции и является составной частью конвейера.

Control unit является цифровым автоматом и может быть реализован с применением микропрограммного автомата либо на комбинационной логике ( "жесткой логике ").

Необходимо обратить внимание, что в процессоре RISC-V манипуляции с данными производятся только из регистрового файла. Для манипуляции с данными их предварительно необходимо загрузить из памяти в регистры регистрового файла, выполнить операцию, а затем если это предусмотрено кодом инструкции разместить обратно в памяти.

В данной архитектуре обращение к памяти возможно только с помощью двух специальных команд: load (lw) и store (sw). В английской транскрипции данный метод организации работы с памятью называют Load/Store architecture.

Команда load (загрузка) обеспечивает считывание данных из основной памяти и занесение их в регистр процессора (в команде обычно указывается адрес ячейки памяти и номер регистра)

Пересылка информации в противоположном направлении производится командой store (сохранение).