Архитектура процессоров

Для рассматриваемой архитектуры также выполним вычисление чисел Фибоначчи. В листинге 7.5 приведен пример на языке ассемблера

# Начальные значения fib(0) = 0, fib(1) = 1

add x1, x0, x0 # в x1 заносим 0

add x2, x0, x1 # в x2 заносим 1

# Переменная n для хранения входящего значения

add x3, x10, x0 # x3 = n

# Проверка n (0 и 1)

add x4, x0, x0 # x4 = 0 ; fib(0)

beq x3, x4, return_zero # Если n == 0, переход к return_zero

add x4, x0, x0 # x4 = 0 ; переменная для счетчика

addi x4, x4, 1 # x4 = 1 ; стартовый индекс (fib(1))

next_fib:

add x5, x1, x2 # x5 = fib(n-1) + fib(n-2)

add x1, x2, x0 # fib(n-1) = fib(n)

add x2, x5, x0 # fib(n) = новый fib(n)

addi x4, x4, 1 # увеличиваем счетчик

bne x4, x3, next_fib # если счетчик не равен n, переходим к next_fib

finish:

add x10, x2, x0 # возвращаем результат в a0

return_zero:

add x10, x0, x0 # возвращаем 0

Листинг

7.5.

Организация и работа с памятью в RISC-V. Стековая память

Стековая память в архитектуре RISC-V организуется аналогично другим архитектурам с учетом особенностей RISC-V. Как отмечалось выше основное назначение стека - временное хранение переменных при вызове функции, а также хранение адресов возврата из функций (подпрограмм).

Стек растет в выделенной для него области памяти от старших адресов к младшим. При добавлении новых данных в стек адрес стека уменьшается.

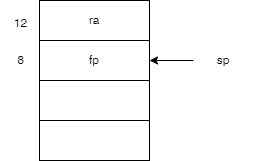

Для работы со стеком в файле регистров выделен регистр x2, имеющий алиас sp - указывает на вершину стека.

В дополнение к sp может применятся регистр fp (frame pointer), который помогает отслеживать основание текущего фрейма функции, что облегчает доступ к локальным переменным и параметрам.

Операции со стеком:

При входе в функцию устанавливается фрейм указателя fp и выделяется место для локальных переменных (пример приведен в листинге 7.6, а работа показана на рисунке 7.11).

addi sp, sp, -16; уменьшить указатель стека для выделения 16 байт

sw ra, 12(sp); сохранить адрес возврата

sw fp, 8(sp); сохранить предыдущий фрейм указателя

addi fp, sp, 16; установить новый фрейм указателя

Листинг

7.6.

При завершении работы функции указатели восстанавливаются, и стек возвращается в прежнее состояние (листинг 7.7).

addi sp, sp, 16; восстановить указатель стека

lw ra, 12(sp); восстановить адрес возврата

lw fp, 8(sp); восстановить предыдущий фрейм указателя

ret; возврат из функции

Листинг

7.7.

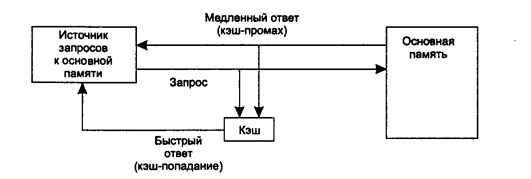

Кэш память

Кэш - небольшая быстрая память относительно основной памяти ЭВМ, расположенная близко к процессору, чаще всего на одном с ним кристалле.

Кэш копирует оперативную память не отдельными байтами, а областями, называемыми кэш-линиями. Если в случае обращения процессора к данным они оказываются в кэше, то это называется кэш-попаданием, если же их не оказывается в кэше, то это называется кэш-промахом.

В случае кэш-попадания запрос процессора в память обрабатывается значительно быстрее чем в случае кэш-промаха, так как кэш расположен гораздо ближе к процессору, чем оперативная память.

Кэш-память включает несколько уровней, каждый из которых имеет свои характеристики:

-

Уровень L1

Разделение на кэш инструкций и кэш данных:

- I-cache (кэш инструкций): Хранит инструкции, которые процессор будет выполнять. Обычно реализуется с невысокой латентностью доступа.

- D-cache (кэш данных): Хранит данные, необходимые для выполнения программ.

Размер: Обычно L1-кэш имеет небольшой размер, диапазон обычно от 16 KB до 128 KB. Этот уровень кэша имеет очень высокую скорость доступа.

-

Уровень L2

Единый или разделённый L2-кэш может быть либо единым для инструкций и данных, либо разделённым на I-cache и D-cache.

Объем больший по сравнению с L1-кэшем и может варьироваться от 256 KB до нескольких МБ. Он медленнее чем L1, но все ещё намного быстрее, чем доступ к основной памяти.

На рисунке 6.12 приведена пример схемы кэш-памяти.

Ассоциативность кэша определяет, сколько мест (строк) может использоваться для хранения определённого блока данных.

Прямой кэш: каждый блок памяти может быть помещён только в одно определённое место в кэше. Это простейшая и наиболее быстрая организация.

Ассоциативный кэш: позволяет хранить блоки данных в нескольких местах. Например, 4-х ассоциативный кэш может разместить данные в четырёх различных местах, что снижает вероятность конфликтов при хранении.