Архитектура процессоров

Полностью ассоциативный кэш: данные могут храниться в любом месте кэша, что повышает гибкость, но требует сложных алгоритмов поиска.

Устройство кэш-строк:

- тег: уникальный идентификатор, относящийся к блоку данных в основной памяти. Используется для определения принадлежности данных к конкретному блоку.

- данные: хранимые данные.

- контрольная информация: например, биты валидности (valid bits) и биты "изменения" (dirty bits), которые показывают, были ли данные изменены.

Существуют следующие алгоритмы кэширования

-

Замещение: когда кэш заполнен и необходимо загрузить новый блок, используется алгоритм замещения:

- LRU (Least Recently Used): Удаляет наименее использованные блоки.

- FIFO (First In First Out): Удаляет самые старые блоки.

- Random: Случайным образом выбирает блок для удаления.

-

Запись: при записи данных в кэш могут использоваться различные стратегии:

- Write-Through - данные сразу записываются как в кэш, так и в основную память. Это гарантирует целостность данных, но может быть медленнее.

- - Write-Back - данные записываются в кэш, а в основную память только при необходимости (например, при замещении). Это может повысить производительность, но потребует дополнительной логики для поддержания согласованности данных.

Кэш-память основывается на двух основных принципах локальности:

- Локальность по времени. Если данные были использованы в последнее время, они с большой вероятностью будут использованы снова.

- Локальность по пространству. Если данные были использованы, то данные, находящиеся рядом в с ними в памяти также имеют высокую вероятность быть использованными.

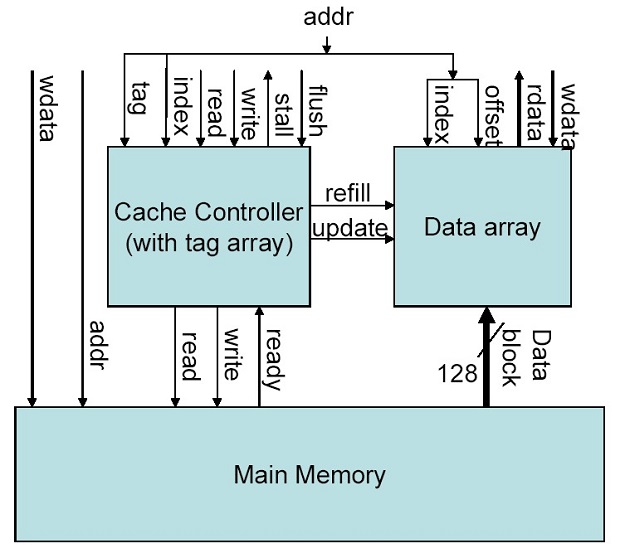

При разработке собственных решений на архитектуре RISC-V в зависимости от проекта применяется создание блока кэш-памяти. Относительно ядра процессора кэш будет внешним устройством и внедрение потребует создание блока контроллера кэш - памяти. На рисунке 7.13 приведен пример одной из разработок для RISC-V на FPGA с блоком кэш-памяти [7]. Для приведенного блока разработчиком определены следующие характеристики:

- объем кэш памяти: 512 байт;

- размер блока кэш-памяти: 16 байт;

- адрес памяти: 10 бит;

- смещение: 2 бита;

- индекс данных: 5 бит;

- тэг: 3 бита.

Тактирование процессора

Тактирование процессора определяет порядок его функционирования, обеспечивая синхронность процессов, выполнения операций и управления работой всех блоков.

Цикл тактирования время между двумя последовательными пиками тактового сигнала. Это время, за которое процессор может выполнить одно или несколько действий.

Критически длинный путь - время, отводимое на исполнение самой долгой инструкции.

В большинстве процессоров, включая RISC-V, выполнение инструкций делится на несколько этапов, каждый из которых обычно занимает один тактовый цикл. Эти этапы, как было отмечено в начале раздела, могут включать:

- Выборка инструкции (Fetch). Процессор считывает следующую инструкцию из памяти. Используется счетчик инструкций (PC), указывающий на адрес инструкции.

- Декодирование (Decode). Инструкция декодируется для определения, какие действия следует выполнить и какие регистры или ячейки памяти необходимы. Активируются связи для взаимодействия операндов.

- Исполнение (Execute). Выполняются операции, указанные в инструкции, часто с использованием арифметико-логического устройства (ALU).Например, в случае арифметических операций производится математическое вычисление.

- Запись результата (Write Back). Результат выполнения операции записывается обратно в регистры или память.

Выделяют однотактные, многоактные и конвейерные процессоры.

Однотактный (single-cycle) - процессор выполняет всю команду за один такт. Принцип работы легко объяснить, а устройство управления довольно простое. Из-за того, что все действия выполняются за один такт, эта микроархитектура не требует дополнительных регистров, требуемых для работы процессора, но недоступных для использования программистом). Однако, длительность такта ограничена самой медленной командой, использующей самый длинный критический путь.

Основным преимуществом однотактной микроархитектуры является простота понимания ее работы. К минусам можно отнести: относительно высокие аппаратные затраты из-за использования дополнительных сумматоров и раздельной основной памяти (гарвардская архитектура), низкая тактовая частота из-за длинного критического пути, так как разные инструкции проходят разный путь, скорость работы ограничена скоростью самой медленной инструкции.

Многотактный процессор (multi-cycle) - выполняет команду за несколько более коротких тактов. Простым командам нужно меньше тактов, чем сложным. Вдобавок, многотактная микроархитектура уменьшает количество необходимой аппаратуры путем повторного использования таких "дорогих " блоков, как сумматоры и блоки памяти.

Многотактная микроархитектура предполагает использование буферных регистров, с целью уменьшения критического пути и поднятия таковой частоты. При этом каждая инструкцию будет выполняться несколько более коротких тактов, используя разное количество тактов для реализации разных инструкций.

Конвейерные процессоры увеличивают производительность, позволяя нескольким инструкциям прокладывать свой путь через процессор в одно и то же время. При применении данной микроархитектуры процессор начинает декодировать новую инструкцию, в то время как предыдущая ожидает результатов. В этом случае до нескольких инструкций может находиться в обработке одновременно, позволяя процессору выполнять вычисления в несколько раз быстрее.

Приведенный на рисунке 7.8 процессор, который проектируется в данном курсе является однотактным. В дополнительной литературе [1] приводятся примеры многотактных процессоров и организации конвейера.