Архитектура процессоров

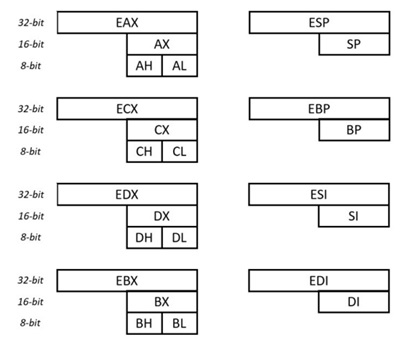

С точки зрения программиста в Intel архитектуре выделяются общие поименованные регистры, которые применяются при разработке программ на языке ассемблера. Данные регистры называют регистрами общего назначения (РОН). К некоторым из них можно обращаться секциями: байтом, словом двойным словом (для 32-разрядной x86 архитектуры). На рисунке 7.5 приведены поименованные 32-х разрядные регистры Intel x86 и форматы взаимодействия с частями данных регистров. При работе с 64-х разрядной архитектурой процессора префикс заменяется на букву R. Регистры общего назначения являются основой для разработки программ и позволяют решать основные задачи по обработке данных, таких, как хранение операндов для арифметических и логических операций, операндов вычисления адресов ячеек памяти, указателей на переменные в памяти.

Несмотря на общий характер данных регистров они всё же используются для определенных целей:

- EAX - регистр аккумулятор. Применяется при работе с арифметическими и логическими операциями, хранит результат операции. Наличие регистра аккумулятора относит процессор к одному из видов процессоров - процессоров с аккумуляторами

- EBX - базовый регистр. Применяется для хранения базового адреса данных в памяти, адресуемой регистром DS;

- ECX - регистр счетчик. Применяется для организации циклов и хранения элементов строковых операций;

- EDX - регистр данных. Хранит промежуточные данные и применяется при работе с арифметико-логическим устройством и операциями ввода вывода;

- ESP - регистр указатель стека. Указывает вершину стека, адресуемого регистром SS.

- EBP - регистр указатель. Применяется для указания базового стекового адреса

- ESI - регистр указатель источника индекса. Указывает на данные, находящиеся в сегменте оперативной памяти, адресуемом регистром DS.

- EDI - регистр указатель индекса получателя данных. Данный регистр указывает на сегмент данных, адресуемый регистром ES.

В 32-х разрядных процессорах архитектуры x86 для управления памятью применяются следующие сегментные регистры:

- CS - регистр сегмента кода. Содержит адрес сегмента, содержащий коды инструкций программы, загружаемой в процессор;

- DS - регистр сегмента данных. Содержит обрабатываемые программой данные;

- SS - регистр сегмента стека. Содержит адрес стека.

Стек (стековая память) - структура данных в оперативной памяти, применяемая для временного хранения содержимого регистров процессора, например, для обработки подпрограммы прерывания. Данные упорядочиваются в стеке последовательно. Существуют следующие виды стеков:

- LIFO - Last input, First output. Данные, поступившие в данный сегмент памяти последними, будут извлечены и удалены первыми;

- FIFO - First input, First output. Данные, поступившие в данный сегмент памяти первыми, будут извлечены и удалены первыми.

Регистр указатель стека ESP фиксирует в себе адрес последних записанных данных.

Отдельно стоит отметить наличие регистра флагов, определяющего состояние процессора, применяемого для управления переходами.

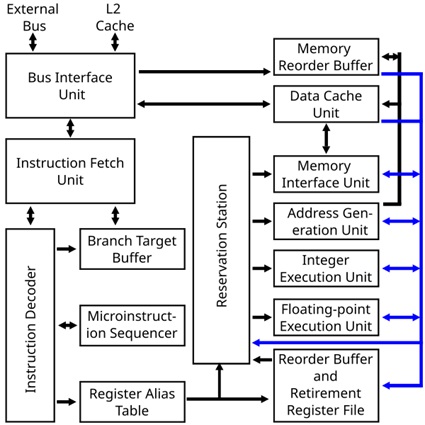

Как видно из описания, x86 процессоры представляют собой сложную организацию с закрытой микроархитектурой. Механизмы управления и параллелизма представляют собой множество цепей управления, соответственно система управления является громоздкой и требует инженерного творчества для обеспечения высокой производительности.

RISC процессоры

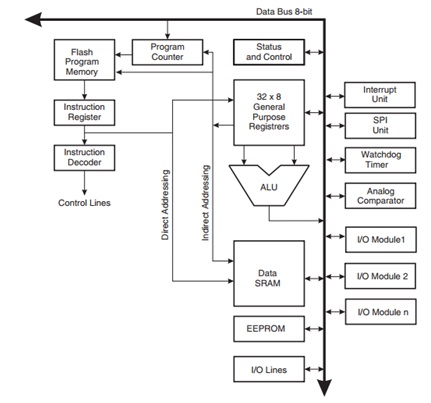

Рассмотрим микроархитектуру RISC на примере восьмиразрядного микроконтроллера Atmega328P (устанавливается на все Arduino UNO отладочные платы). На рисунке 7.6 приведена упрощенная схема данного микроконтроллера со следующими основными блоками:

- Flas Program memory - перепрограммируемая память инструкций;

- Instruction Register (IR) - регистр текущей инструкции;

- Instruction Decoder - дешифратор команд;

- Program Counter (PC) - счетчик адреса инструкций. Указывает на адрес памяти инструкций;

- Status and Control - регистр состояний;

- 32x8 General Purpose Registers - регистры общего назначения, объединенные в регистровый файл;

- Data SRAM - оперативная статическая память данных;

- EEPROM - постоянная память данных;

- I/O Lines - линии соединения процессорного ядра с периферийными модулями.

Расположенные справа модули представляют специфические для каждого микроконтроллера встроенные периферийные устройства, обеспечивающие сбор, прием/передачу данных и сигналов для исполнительных механизмов, т.е порты ввода-вывода данных (I/O Module).

Как видно из схемы память инструкций и данных разделены, соответственно архитектура организации памяти - гарвардская.