|

Здравствуйте! Прошел курс, а где экзамен? Как сертификат получить? Без экзамена? |

Комбинационные схемы

Необходимые материалы для лекции logisim.zip и Quartus.zip.

При проектировании цифровых устройств базовые и производные логические элементы объединяются в более крупные функциональные узлы, именуемые комбинационные и последовательностные схемы.

Комбинационная схема - это цифровая схема, состояние сигналов на выходе которой, зависит от изменения сигналов на его входе.

В данной лекции рассматриваются комбинационные схемы, входящие в микропроцессорные системы, в том числе в процессоры RISC-V, или применяемые для проектирования окружения (обвязки) микропроцессоров.

Дешифратором или декодером (англ. decoder) называют кодирующее устройство, преобразующее двоичный код в унарный. Из всех m выходов дешифратора активный уровень имеется только на одном, а именно на том, номер которого равен поданному на вход двоичному коду.

В то же время существуют другие виды кодирующих устройств, также называемых дешифраторами, например, дешифратор семисегментного индикатора. Реализация данного дешифратора будет рассмотрена в лабораторной работе 2.

Дешифратор используют, когда нужно обращаться к различным цифровым устройствам, и при этом номер (адрес) устройства представлен двоичным кодом.

В таблице 2.1 приведена таблица истинности для дешифратора с выходами 0-7 (на схеме будут обозначены А0-А7), реагирующего на уровни логической "1" на входе. Для получения заданных выходных сигналов необходимо наличие трёхразрядного входа (Х0-Х3).

| Номер декодируемой линии выхода | Сигналы на линиях входа | Сигналы на выходе | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| X2 | X1 | X0 | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 2 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 3 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 4 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 5 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 6 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 7 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

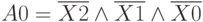

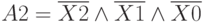

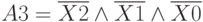

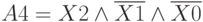

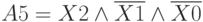

Описать работу дешифратора можно при помощи минтерм (объединение переменных знаком конъюнкции) для каждой выходной функции. Для дешифратора с таблицей истинности, представленной выше будут составлены следующие минтермы:  ;

;  ;

;  ;

;  ;

;  ;

;  ;

;  ;

;  .

.

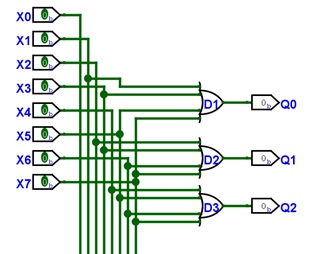

На основании минтерм далее можно реализовать схему. Для каждой функции будет применятся собственный конъюнктор. Линии данных входа Х0-Х2 идут, как прямые, так и инверсные общие для всех конъюнкторов. Каждую функцию образуют одни и те же переменные. На рисунке 2.1 приведена схема функциональная дешифратора в среде Logisim Evolution. При проектировании схемы для примера дешифратора в среде Logisim Evolution применялись элементы "И" (вкладка "Элементы"). Свойства для данного элемента: "Размер элемента" - узкий, "Количество входов" - 3. В поле метка заносится метка для каждого элемента как показано на рисунке 2.1: D4, D5 и т.д. Инверторы D1-D3 находятся во вкладке "Элементы". Для них задается только свойство метка. Входы и выходы для дешифратора находятся в панели быстрого доступа. Данным элементам задается только значение метки, соответствующее имени сигнала.

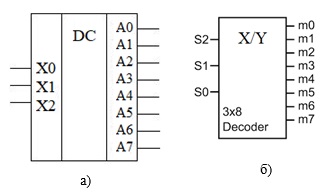

Условное буквенное обозначение дешифратора на схемах - DC (X/Y).

На рисунке 2.2а приведено условно-графическое обозначение (УГО) элемента дешифратора в системе отечественных стандартов ЕСКД (Единая система стандартов конструкторской документации). На рисунке 2.2б приведено УГО элемента в системе ANSI (American national standards institute).

Шифратор, или кодер (англ. encoder), выполняет функцию, обратную дешифратору. Классический шифратор имеет m входов и n выходов. При подаче сигнала на один из входов (обязательно на один, и не более) на выходе узла появляется двоичный код номера возбужденного o выхода. Число входов и выходов такого шифратора связано соотношением  . Шифратор можно использовать, например, для отображения в виде двоичного кода номера нажатой кнопки или положения многопозиционного переключателя.

. Шифратор можно использовать, например, для отображения в виде двоичного кода номера нажатой кнопки или положения многопозиционного переключателя.

Важно! Шифратор может обрабатывать только единичные сигналы на входе. Если на вход данной схемы подать несколько сигналов, то на выходе сформируется неверная кодовая комбинация. В таблице 2.2 приведена таблица истинности для шифратора 8x3, работающего активными высокими уровнями.

| Номер кодируемой линии выхода | Сигналы на линиях входа | Сигналы на выходе | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| X0 | X1 | X2 | X3 | X4 | X5 | X6 | X7 | Q2 | Q1 | Q0 | |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 2 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 3 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| 4 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 |

| 5 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| 6 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 |

| 7 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

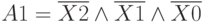

Для проектирования шифратора применяются макстермы для каждой функции выхода. То есть выход шифратора Q0 будет активен для чисел 1 или 3 или 5 или 7. Соответственно сигналы с входов X1, X3, X5, X7 объединяются дизъюнкторами ("ИЛИ"). На рисунке 2.3 приведена функциональная схема в среде Logisim Evolution.