Комбинационные схемы

module interf_dec (input [0:4] SW, output [6:0] HEX); //определение //интерфейсов seven_segment_decoder ex1(.bin(SW), .seg(HEX));//создание экземпляра //дешифратора и связывание интерфейсов endmoduleЛистинг 2.2.

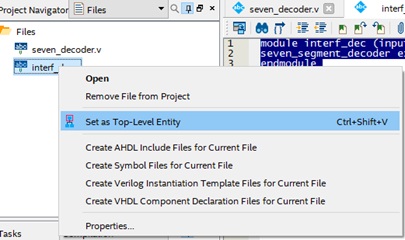

Следующим шагом необходимо определить файл interf_dec файлом верхнего уровня. Для этого в разделе "Project Navigator" основной формы выбрать в ниспадающем списке - Files. Щелкнуть левой кнопкой мыши по файлу, определяемому верхним в иерархии. В контекстном меню выбрать Set as a Top-Level Entity (рисунок 2.37) или нажать комбинацию "горячих клавиш" Ctrl+Shift+V.

Далее необходимо выполнить синтез проекта. Для этого в меню быстрого доступа нажать на кнопку

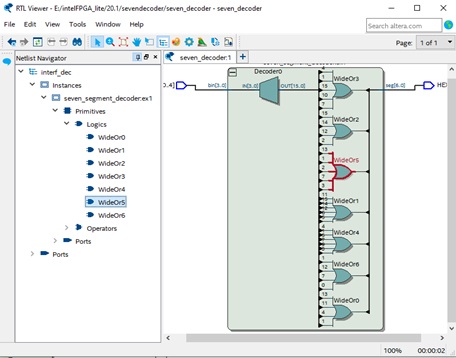

, либо в меню "Processing" - "Start" выбрать Analysis & Synthesis. По окончании моделирования можно просмотреть результат в виде представления на уровне регистровых передач - RTL.Для просмотра данного уровня передач необходимо вызвать в главном меню "Tools" - "Netlis Viewers" - "RTL Viewer". Результат представлен на рисунке 2.38.

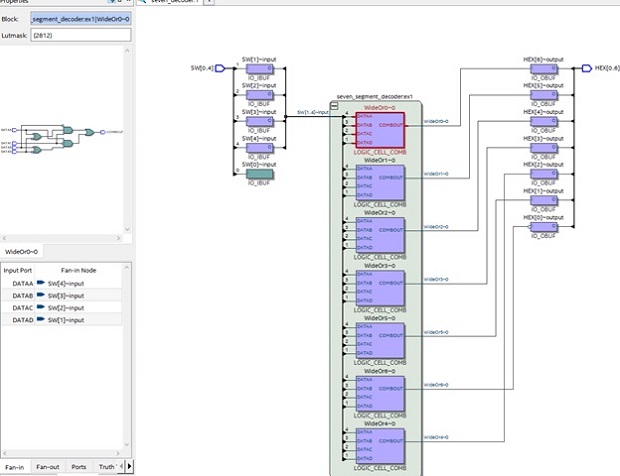

Для просмотра схемы на уровне логических функций можно выбрать "Tools" - "Netlis Viewers" - "Technology Map Viewer" - "Post Mapping" (рисунок 2.39).

Для симуляции работы дешифратора с использованием ModelSim необходимо создать новый каталог, например simulation. Скопировать в него seven_segment_decoder.v. В текстовом редакторе создать файл и сохранить его под именем testbench.v. Данный файл является файлом тестовых сигналов для спроектированного модуля. В данный файл ввести код из листинга 2.3.

module testbench;

reg [3:0] bin; // Входной сигнал (4 бит)

wire [6:0] seg; // Выходной сигнал (7 сегментов)

seven_segment_decoder uut ( // Инстанцирование модуля дешифратора

.bin(bin),

.seg(seg)

);

initial begin

// Печатаем заголовок тестов

$display("Testing Seven Segment Decoder\n");

// Тестируем значения от 0 до 15

for (bin = 0; bin < 16; bin = bin + 1) begin

#10; // Задержка 10 тактов

$display("Input: %b | Output: %b", bin, seg); // Выводим вход и соответствующий выход

end

// Завершение симуляции

$finish;

end

endmodule

Листинг

2.3.

В литературе [3] описаны принципы создания скриптов для управления симуляцией проектов в ModelSim. По аналогии с приведенными скриптами опишем управляющие скрипты для дешифратора. В текстовом редакторе создать файл и сохранить его под именем simulation.tcl.

Набрать код из листинга 2.4.

# создание рабочей библиотеки в симуляторе vlib work # указание компилятору на компилируемые файлы vlog ../testbench.v ../../ seven_segment_decoder.v # открыть тест в симуляторе vsim work.testbench # добавить сигналы для построения диаграммы add wave sim:/testbench/* # запуск симулятора run -all # добавить сигналы на диаграмму построить диаграмму wave zoom fullЛистинг 2.4.

Для исполнения описанного выше файла предлагается создать файл пакетной обработки. В текстовом редакторе создать новый файл, сохранить его под именем start.bat.