Комбинационные схемы

Для выполнения практической работы необходимо в среде Logisim Evolution реализовать функционал микросхемы 4048 (согласно рисунка 2.42). Ниже описывается этап моделирования базовой функциональной схемы микросхемы 4048 без транзисторов на выходе - они заменены на эквивалентный логический элемент ИЛИ-НЕ. Схема проектируется для четырех входов A,B и E,F.

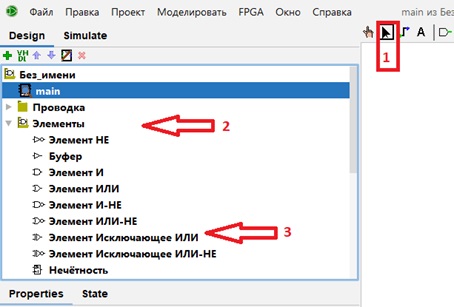

В среде Logisim Evolution (рисунок 2.45), используя указатель 1, выбрать в разделе "Элементы" (2) логический элемент "исключающее или" (3). Разместить элемент на поле, задав параметры как на показано рисунке 2.46.

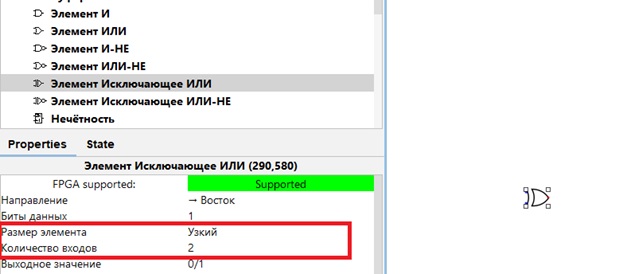

На рисунке 2.46 отображены настройки элементов: размер элемента - узкий (возможно выбрать другой размер). Количество входов - 2. Данные настройки необходимо применить ко всем используемым в проекте элементам, за исключением элемента НЕ. Для него количество входов отсутствует - один вход.

Далее на схему добавить входы и выход. Данные элементы находятся в меню быстрого доступа (рисунок 2.47). Имена входам присвоить согласно функциональной схемы ( рисунок 2.43).

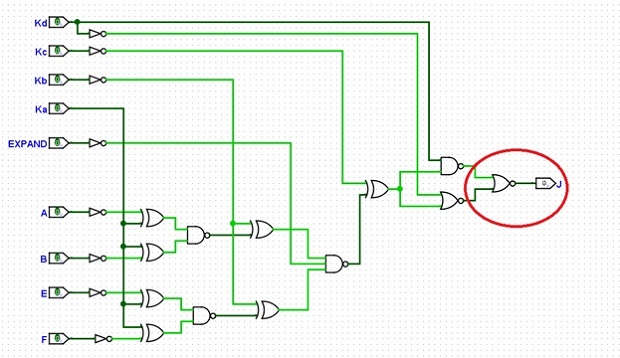

На рисунке 2.48 приведена моделируемая схема для описанного выше количества входов, полностью отражающая модель работы исследуемой микросхемы. После проектирования модели микросхемы 4048, руководствуясь рисунком 2.44, проверить корректность работы таблицы истинности.

Внимание! Из документации к микросхеме следует, что выходы функций объединяются полевыми транзисторами. В случае данной практической работы выходы объединяются схемой ИЛИ-НЕ (NOR) см. рисунок 2.48.

Самостоятельно:

Выполнить моделирование логических функций NOR, OR, AND, NAND по вариантам таблиц истинности для следующих входов управления: Ka,Kb,Kc,Kd (таблица 2.7) в среде Logisim. По аналогии с лабораторной работой 1, на языке описания аппаратуры описать свой вариант комбинационной схемы.

| Вариант | NOR (ИЛИ-НЕ) | OR (ИЛИ) | AND (И) | NAND (И-НЕ) | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Ka | Kb | Kc | Kd | Ka | Kb | Kc | Kd | Ka | Kb | Kc | Kd | Ka | Kb | Kc | Kd | |

| 1,10,19 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

| 2,11,20 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| 3,12,21 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 |

| 4,13,22 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 5,14,23 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 |

| 6,15,24 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 0 |

| 7,16,25 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 |

| 8,17,26 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 9,18,27 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 |

В листинге 2.6 приведен код на языке описания аппаратуры Verilog HDL для схемы, приведенной на рисунке 2.48. Входы, над которыми производятся логические операции, разделены на два четырехразрядных входа А и В. Код можно реализовать проще, видоизменяя функции, так как в примере операция выполняется побитно с описанием каждого бита данных.

module mmc4048 (input wire [3:0] A,B, input Ka,Kb,Kc,Kd, output reg J);

always @(*)//анализируем все входы

case ({Ka,Kb,Kc,Kd}) //проверка сигналов управления

4'b0000: J=~((A[3]|A[2]|A[1]|A[0])|(B[3]|B[2]|B[1]|B[0]));// операция NOR

4'b0010: J=((A[3]|A[2]|A[1]|A[0])|(B[3]|B[2]|B[1]|B[0]));//операция OR

4'b0100: J=(A[3]|A[2]|A[1]|A[0])&(B[3]|B[2]|B[1]|B[0]);//операция OR_AND

4'b0110: J=~((A[3]|A[2]|A[1]|A[0])&(B[3]|B[2]|B[1]|B[0]));//операция OR_NAND

4'b1000: J=((A[3]&A[2] &A[1] &A[0]) & (B[3] &B[2] &B[1] &B[0]));//операция AND

4'b1010: J=(~(A[3] &A[2] &A[1] &A[0])|~(B[3] &B[2] &B[1] &B[0]));//операция NAND

4'b1100:J=~((A[3] &A[2] &A[1] &A[0])|(B[3] &B[2] &B[1] &B[0]));//операция //AND_NOR

4'b1110: J=((A[3] &A[2] &A[1] &A[0])|(B[3] &B[2] &B[1] &B[0]));//операция AND_OR

default: J=1'b0;

endcase

endmodule

default: J=1'b0;

endcase

endmodule

Листинг

2.6.

На рисунке 2.49 приведено представление описанной в листинге 2.6 схемы на уровне регистровых передач (RTL).