|

Здравствуйте! Прошел курс, а где экзамен? Как сертификат получить? Без экзамена? |

Комбинационные схемы

В этом окне приведена итоговая информация предыдущих шагов NPW, а также информация по условиям работы выбранного кристалла. Нажатие на кнопку Finish завершит работу NPW. Если теперь открыть окно навигатора проекта, то на странице Hierarchy появится тип выбранного кристалла ПЛИС и имя модуля верхнего уровня, а на странице Files - добавленные к проекту файлы.

Утилита NPW позволяет на каждом шаге своего выполнения вернуться к предыдущим шагам, и в случае необходимости, скорректировать выполненные действия.

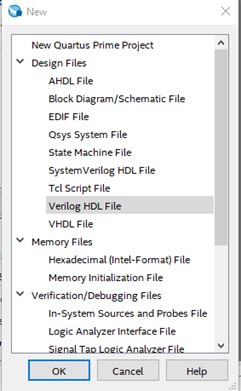

Для описания дешифратора необходимо кликнуть левой кнопкой мыши по "File" на панели меню Quartus. В открывшемся окне выбрать Verilog HDL File (рисунок 2.36).

В редакторе кода ввести код из листинга 2.1.

module seven_segment_decoder (

input [3:0] bin, // 4-битный вход (двоичное представление числа)

output reg [6:0] seg // 7-сегментный выход

);

always @(*) begin

case (bin)

4'b0000: seg = 7'b0000001; // 0

4'b0001: seg = 7'b1001111; // 1

4'b0010: seg = 7'b0010010; // 2

4'b0011: seg = 7'b0000110; // 3

4'b0100: seg = 7'b1001100; // 4

4'b0101: seg = 7'b0100100; // 5

4'b0110: seg = 7'b0100000; // 6

4'b0111: seg = 7'b0001111; // 7

4'b1000: seg = 7'b0000000; // 8

4'b1001: seg = 7'b0000100; // 9

4'b1010: seg = 7'b0001000; // A

4'b1011: seg = 7'b1100000; // B

4'b1100: seg = 7'b0110001; // C

4'b1101: seg = 7'b1000010; // D

4'b1110: seg = 7'b0110000; // E

4'b1111: seg = 7'b0111000; // F

default: seg = 7'b1111111; // Все сегменты выключены

endcase

end

endmodule

Листинг

2.1.

Сохранить файл под тем же именем, что и имя модуля -seven_segment_decoder.v.

Следующим этапом создать новый Verilog HDL файл, который будет верхним в иерархии файлов для данного проекта. Сохранить файл под именем interf_dec.v. В редакторе кода ввести код из листинга 2.2