Комбинационные схемы

Контрольные вопросы

- В чем разница между шифратором и приоритетным шифратором?

- Что такое каскадирование элементов?

- Возможно ли реализовать схему дешифратора семисегментного индикатора меньше приведенной?

- Как может проявляется ошибка на шифраторе при одновременной подаче на вход нескольких сигналов?

Литература

- Потемкин И.С. Функциональные узлы цифровой автоматики. - М.: Энергоатомиздат, 1988.- 320с.: ил. (С.96)

- С. Харрис, Д. Харрис. Цифровая схемотехника и архитектура компьютера RISC-V/ пер. с англ. В.С. Яценкова, А.Ю. Романова; под. ред. А.Ю. Романова.-М.: ДМК Пресс, 2022. - 810 с.: ил. (с 116-117, 154-158.

- Романов А.Ю. Цифровой синтез RISC-V. - М.: ДМК Пресс, 2024. - 636с.: ил.

- https://www.promelec.ru/articles/segmentnye-tsifrovye-indikatory-foryard-neizmennoe-kachestvo-pri-optimalnoj-tsene/

- http://phg.su/basis2/X123.HTM

- http://www.rotr.info/electronics/mcu/seven_segment.htm

- Паспорт для микросхемы MMC4048 [Электронный ресурс] http://www.datasheetcatalog.com/datasheets_pdf/M/M/C/4/MMC4048.shtml (дата обращения 02.08.2024)

Дополнительная литература

- Микушин А.В. Цифровые устройства и микропроцессоры: учебн. пособие. - СПб.: БХВ-Петербург, 2010 - 832 с.: ил. (С. 78 - 106, 191).

Приложение 2. Описание ряда комбинационных схем на языке Verilog

В языке описания аппаратуры Verilog существует два способа описания аппаратуры:

- Структурный (может встречаться схемный или логический) при котором описывается явный состав логических элементов и внутренних связей между ними;

- Поведенческий (функциональный метод) способ преобразования сигналов описывается при помощи специальных конструкций без явного описания внутренней структуры устройства. Выражается в виде функций, зарезервированных в языке Verilog HDL.

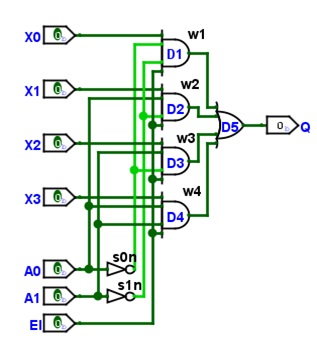

Разберем различия в описаниях аппаратуры данными методами на примере мультиплексора, приведенного на рисунке 2.7. Для этого добавим на рисунок дополнительные подписи у элементов D1,D2,D3,D4: w1, w2, w3, w4. Выходы инвертора входа А0 подпишем s0n, у инвертора входа А1 - s1n (рисунок 2.50).

Теперь объявим входы и выходы непосредственно в конструкции module. Имена присвоим те же, что и на рисунке 2.50:

module mux_4(input X0, X1, X2, X3, A0, A1, EI, output Q);

Объявим внутренние цепи - выходы логических элементов, применяемых в схеме:

wire s0n,s1n; wire w1,w2,w3,w4;

Далее получим инверсии адресных входов:

not n0(s0n,A0); // инверсия "имя", "имя выхода цепи", вход not n1(s1n,A1);

Следующим шагом реализуем логические операции для входов X0-X3, управляющего сигнала EI, адресных входов A0,A1 и их производных - внутренних сигналов. Получая внутренние цепи w1-w4:

and and1(w1,X0,s0n,s1n,EI); and and2(w2,X1,A0,s1n,EI); and and3(w3,X2,A1,s0n,EI); and and4(w4,X3,A0,A1,EI);

Результирующий выход Q является объединением внутренних цепей w1-w4 через дизъюнкцию:

or or1(Q,w1,w2,w3,w4);

В листинге 2.7 приведен исходный код данного мультиплексора

module mux_4(input X0, X1, X2, X3, A0, A1, EI, output Q); wire s0n,s1n; wire w1,w2,w3,w4; not n0(s0n,A0); not n1(s1n,A1); and and1(w1,X0,s0n,s1n,EI); and and2(w2,X1,A0,s1n,EI); and and3(w3,X2,A1,s0n,EI); and and4(w4,X3,A0,A1,EI); or or1(Q,w1,w2,w3,w4); endmoduleЛистинг 2.7.