Опубликован: 17.03.2025 | Доступ: свободный | Студентов: 0 / 0 | Длительность: 07:30:00

Лекция 2:

Комбинационные схемы

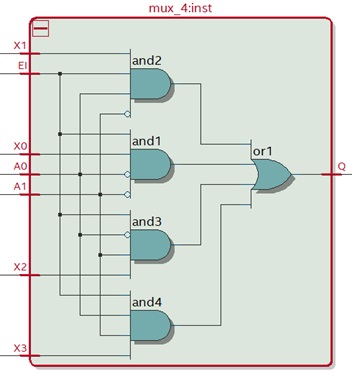

На рисунке 2.51 показан RTL вид полученной схемы.

Далее опишем мультиплексор, но уже поведенческим методом. Вход А в данном случае будет объявлен как двухразрядная шина:

module mux2to1 (input X0, X1, X2, X3, EI, input wire[1:0]A, output Q);.

Объявим внутреннюю шину для прямого выхода данных:

wire mux_output;

Связываем внутреннюю шину с входами, в зависимости от адреса:

assign mux_output = (A == 2'b00) ? X0 :

(A == 2'b01) ? X1 :

(A == 2'b10) ? X2 :

(A == 2'b11) ? X3 : 1'b0; // Значение по умолчанию.

Выходное состояние будет зависеть от входа управления EI через выражение:

assign Q = ~EI ? ~mux_output : mux_output;.

Итоговый листинг имеет вид:

module mux2to1 (input X0, X1, X2, X3, EI,input wire[1:0]A, output Q);

wire mux_output;

assign mux_output = (A == 2'b00) ? X0 :

(A == 2'b01) ? X1 :

(A == 2'b10) ? X2 :

(A == 2'b11) ? X3 : 1'b0;

assign Q = ~EI ? ~mux_output : mux_output;

endmodule

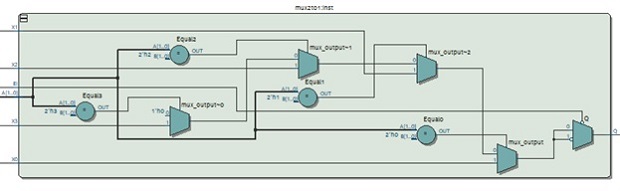

На рисунке 2.52 показан RTL вид полученной схемы.

Ниже в листинге 2.8 приведен пример поведенческого описания для шифратора, в листинге 2.9 приведен код для дешифратора.

module encoder3 (

input wire [7:0] in, // 8-битный входной сигнал

output reg [2:0] out, // 3-битный выходной сигнал

output reg valid // Сигнал активности выхода

);

// Определяем поведение шифратора

always @(*) begin

case (in)

8'b00000001: begin out = 3'b000; valid = 1; end

8'b00000010: begin out = 3'b001; valid = 1; end

8'b00000100: begin out = 3'b010; valid = 1; end

8'b00001000: begin out = 3'b011; valid = 1; end

8'b00010000: begin out = 3'b100; valid = 1; end

8'b00100000: begin out = 3'b101; valid = 1; end

8'b01000000: begin out = 3'b110; valid = 1; end

8'b10000000: begin out = 3'b111; valid = 1; end

default: begin out = 3'b000; valid = 0; end // Сигнал по умолчанию

endcase

end

endmodule

Листинг

2.8.

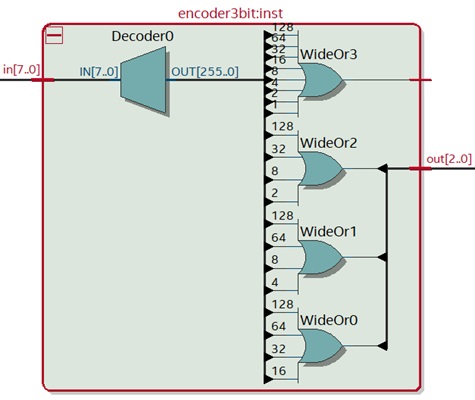

На рисунке 2.53 приведено RTL представление шифратора

module decoder3to8 (

input wire [2:0] in, // 3-битный входной сигнал

output reg [7:0] out // 8-битный выходной сигнал

);

// Определяем поведение дешифратора

always @(*) begin

// Сбрасываем выход на нули

out = 8'b00000000;

// Устанавливаем один бит в 1 в зависимости от входного сигнала

case (in)

3'b000: out[0] = 1'b1;

3'b001: out[1] = 1'b1;

3'b010: out[2] = 1'b1;

3'b011: out[3] = 1'b1;

3'b100: out[4] = 1'b1;

3'b101: out[5] = 1'b1;

3'b110: out[6] = 1'b1;

3'b111: out[7] = 1'b1;

default: out = 8'b00000000; // В случае ошибки сбрасываем на нули

endcase

end

endmodule

Листинг

2.9.

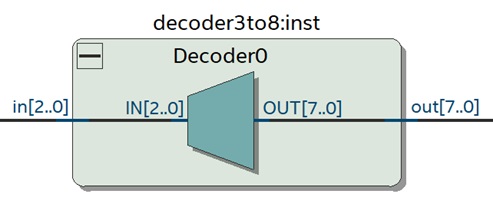

На рисунке 2.54 приведено RTL представление дешифратора