Последовательностная логика. Счетчики

Лабораторная работа 5. "Проектирование конечного автомата приемопередатчика"

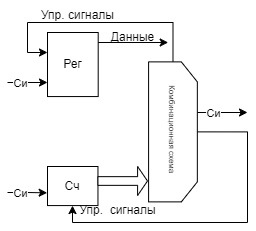

Цель лабораторной закрепить навыки работы со счётчиками и регистрами через реализацию конечного автомата. Разрабатываемое устройство представляет собой простой последовательный интерфейс передачи данных. На рисунке 5.11 приведена блок-схема проектируемого устройства. На схеме счетчик (Сч) выполняет функцию памяти состояния. Комбинационная схема реализует формирование унарных управляющих сигналов, которые обеспечивают переключение состояний счетчика и регистра (Рег).

В проектируемом устройстве байт данных с внутренней шины данных последовательно передается в приемник по двухпроводной линии: данные и синхронизация. Канал передачи данных является однонаправленным.

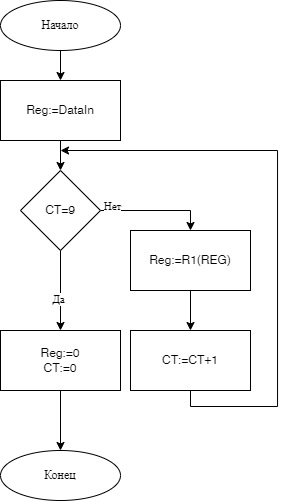

На рисунке 5.12 приведён алгоритм работы передающего устройства. При старте устройства первым тактом осуществляется параллельная загрузка данных в регистр. Со второго такта по 9 осуществляется формирование сигналов сдвига данных в регистре. Десятым тактом происходит останов работы устройства и установка регистра и счетчика в начальное состояние.

На рисунке 5.13 приведена схема функциональная передатчика. На схеме D1 - восьмиразрядный сдвиговый регистр, принимающий параллельные данные и побитно отправляющий их с старшего разряда. На счетчике D5 реализована память состояний. Счетчиком управляет D-триггер D6. При подаче на асинхронный вход S триггера сигнала Start, с входа счетчика R снимается сигнал, блокирующий его работу. На вход управления М1/М2 подан лог. &0 & (применен элемент константа). Счетчик работает в режиме счета, параллельная загрузка не производится. На входы М3/М4 и G5 подан сигнал лог &1 &. Счетчик работает в режиме суммирующего. Вход синхронизации подключен к тактовому генератору. Дешифратор D2 обеспечивает формирование унарных сигналов управления (комбинационная схема). Выход 0 -удерживает регистра D1 в сброшенном состоянии. Сигнал 1 - обеспечит управляющий импульс для параллельной загрузки данных в регистр. Выходы с 2 по 9 через дизъюнктор ( &ИЛИ &) D3 обеспечивают формирование управляющего сигнала сдвига регистра D1. Параллельно с этим формируется управляющий сигнал на элемент D4 - управляющий вентиль линии синхронизации последовательной шины. Десятый выход дешифратора сбрасывает триггер управления D6 через асинхронный вход R, сбрасывая и останавливая работу устройства.

Для упрощения проектирования применяется элемент &тоннель &. Данный элемент применяется для присвоения имен проводников, тем самым не требуется строить на схеме множество линий. Система моделирования определяет, что проводники и шины с одинаковыми именами принадлежат к одной группе линий. Применение тоннелей позволяет упростить визуальное проектирование и восприятие схем, не нагромождая их проводниками. Подобные элементы применяются в различных средах проектирования, начиная от встраиваемых систем, заканчивая интегрированными системами проектирования принципиальных схем и печатных плат. Элемент &тоннель & расположен в разделе &Проводка &. Его основные свойства: &Метка & - имя, присваиваемое проводникам; &Шрифт метки & - определяет размер текста и самого тоннеля; &Биты данных & - разрядность.

На схеме имена тоннелей имеют следующее назначение:

- С - clock, синхронизация цепей в передающем устройстве;

- R - reset, сброс;

- L - load, сигнал параллельной загрузки данных;

- S - shift, сигнал сдвига в регистре передающего устройства;

- S1 - shift, сигнал сдвига в регистре приемного устройства;

- O - output, сигнал последовательной линии передачи данных;

- CLK - clock, сигнал синхронизации приемного устройства.

На рисунке 5.14 приведена вторая часть схемы - приемное устройство. Регистр D7 выполняет функции последовательно-параллельного регистра, принимая данные с линии O. Счетчик D10 синхронизируется вместе с регистром по линии CLK. Дешифратор D8 обеспечивает формирование только двух импульсов. Выходы 0 и 9 дешифратора через элемент D9 (ИЛИ-НЕ) формируют управляющий сигнал S1 для последовательного сдвига данных в регистре D7.