Последовательностная логика. Триггеры

| R | S | Q(t) | Q(t+1) | Пояснения |

|---|---|---|---|---|

| 0 | 0 | 0 | X | Запрещенное состояние |

| 0 | 0 | 1 | X | |

| 0 | 1 | 1 | 0 | Режим сброса |

| 0 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 1 | Режим установки |

| 1 | 0 | 1 | 1 | |

| 1 | 1 | 0 | 0 | Режим хранения |

| 1 | 1 | 1 | 1 |

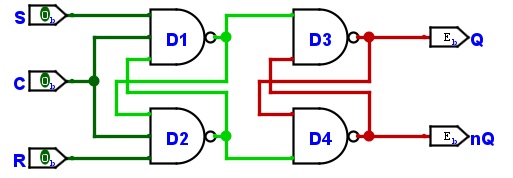

Для защиты триггера от возникновения запрещенных состояний, например при помехах, в схему вводится буферный элемент, включаемый также по схеме триггера. При вводе буферной схемы меняется уровень срабатывания входных сигналов. В схеме, приведенной на рисунке 3.7, уровнем срабатывания будет являться лог. "1". Элементы D3-D4 являются непосредственно триггером, а на элементах D1, D2 работает механизм, ограничивающий реакции на одном из входов, сигнал на котором появляется позже. Данный механизм обеспечивается за счет того, что обратная связь обеспечивает наличие устойчивого состояния.

Для повышения надёжности триггеров применяется дополнительный вход управления, называемый синхросигналом С (clock). В принципе цифровые устройства с памятью, микропроцессорные системы подразумевают наличие синхронизации. Цифровые узлы и периферийные устройства, интерфейсы связи по большей части работают синхронно. Синхронизация обеспечивает качество и надежность обмена данными. В дополнительной литературе [1,2] можно подробно ознакомиться с описанием генераторов синхросигналов и построение систем синхронизации.

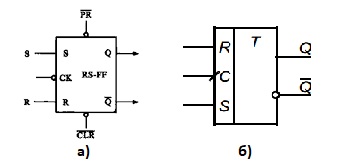

На рисунке 3.8 приведена функциональная схема синхронного SR-триггера. Для его создания применяются элементы 3И-НЕ (D1, D2). Третий вход данных элементов будет объединен и подключен к элементу вход. Его метка присвоено значение "С". На рисунке 3.9 приведено условно-графическое обозначение синхронного SR-триггера в ANSI (рисунок 3.9а ) и ЕСКД (рисунок 3.9б ).

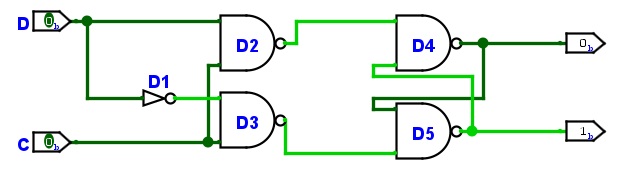

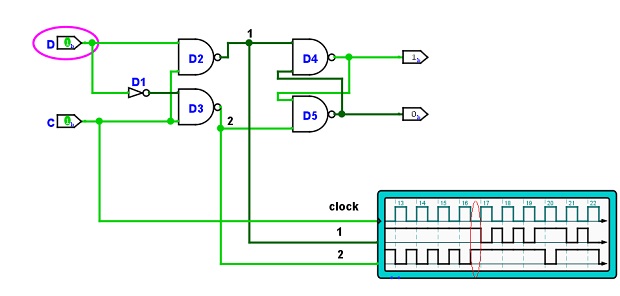

Следующим видом триггеров, является D-триггер, он же триггер, управляемый уровнем синхросигнала. Также встречается в литературе определение "защёлка" или "latch". Ещё один вариант названия - DC-триггер и расшифровывается как С - clock, D - delay (в некоторых источниках можно встретить как data, что в принципе тоже верно по отношению к его функционалу). На рисунке 3.10 показан универсальный способ построения синхронного D-триггера на базе SR триггера.

На элементах D4, D5 реализована ячейка SR-триггера. На элементах D2, D3 реализована схема управления записью в SR-триггер. Элемент D1 обеспечивает инверсию на входе D3, тем самым обеспечивая установку триггера в сброшенное состояние.

В таблице 3.3 приведена таблица истинности для рассматриваемого триггера

| C | D | Q(t) | Q(t+1) | Пояснения |

|---|---|---|---|---|

| 0 | X | 0 | 0 | Режим хранения |

| 0 | X | 1 | 1 | |

| 1 | 0 | X | 0 | Режим записи (0) |

| 1 | 1 | X | 1 | Режим записи (1) |

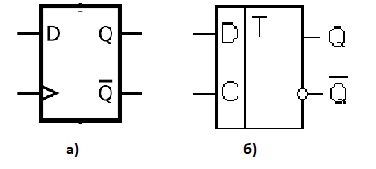

На рисунке 3.11а приведено условно-графическое обозначение синхронного D-триггера в ANSI, а на рисунке 3.11б для ЕСКД.

Для проверки работы схемы в меню "Моделировать" необходимо выбрать "Такты включены". В открывшемся диалоговом окне (рисунок 3.12), выбрать вход С.

Частота синхросигналов задается в меню "Моделировать" - "Тактовая частота".

На примере данного триггера можно рассмотреть еще один вид неверного работа цифровых цепей - "гонка сигналов" (race condition).

Гонка (состязание) сигналов несоответствие сигналов на выходе, вызванное переходными процессами в цепях устройств.

Для наблюдения данной ошибки добавим в схему виртуальный осциллограф. Данный инструмент находится во вкладке "Input/Output Extra" и называется "Цифровой осциллятор". На рисунке 3.13 приведен данный инструмент, где цифрами обозначены: 1 - тактовый вход, подключается к тактовому входу; 2 - вход для измеряемых сигналов.

Основные свойства:

- "Количество входов" - количество измеряемых показаний;

- "Число состояний" - максимальное количество попадающих на экран тактов;

- "Линия фронтальных часов" - реакция на синхросигнал тактового входа;

- "Показать атрибуты часов" - отображения параметров синхросигнала с тактового входа.

На рисунке 3.14 приведена работа триггера с отслеживанием изменения сигналов в контрольных точках 1 и 3. На осциллографе красным выделен переходный процесс, который возникает из-за задержки прохождения сигнала в цепи D1-D3 относительно элемента D3.

Для устранения ошибок гонки сигналов триггеры делают двухступенчатыми. Двухступенчатый триггер состоит из двух триггеров: M-master (ведущий), S - slave (ведомый). Такой триггер именуется MS в условно-графическом обозначении в поле функции пишется ТТ.