Последовательностная логика. Регистры

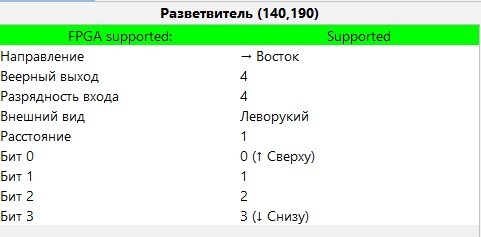

Далее будут выполнены соединения входов D каждого триггера в разветвитель как показано на рисунке 4.6. Верхний триггер будет определяется младшим и подключается к проводу 0, а нижний - старший, подключается к проводу 3 разветвителя.

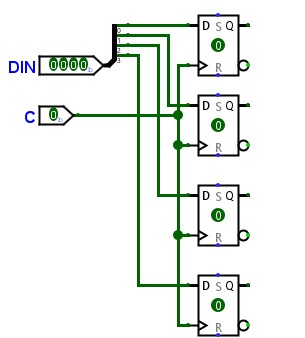

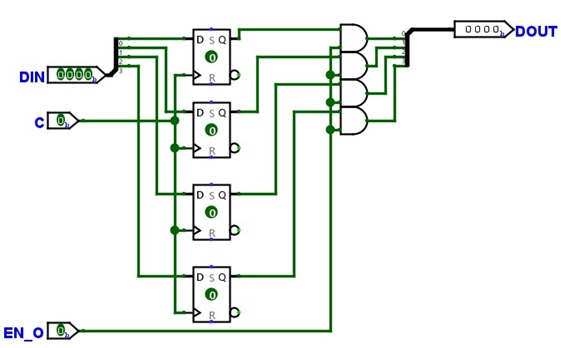

Далее прямые выходы Q триггеров подключим к предварительно размещенным четырем двухвходовым элементам "И". Один вход каждого элемента "И" будет объединен и подключен к добавленному входу EN_O. Выходы элементов "И" заведем также в шину (разветвитель). В данном случае разветвителю необходимо изменить свойство "Направление" на "Запад".

Следующим шагом требуется разместить выход с разрядность 4. Свойству "Метка" присвоить - "DOUT". Входы S и R триггеров оставить неподключенными. Итоговая функциональная схема регистра защелки приведена на рисунке 4.7.

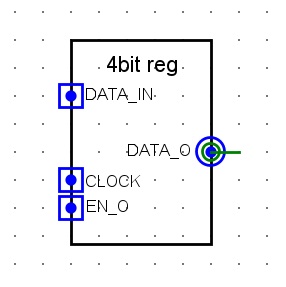

Перейдя в редактор внешнего вида, сформируем графическое обозначение регистра (рисунок 4.8).

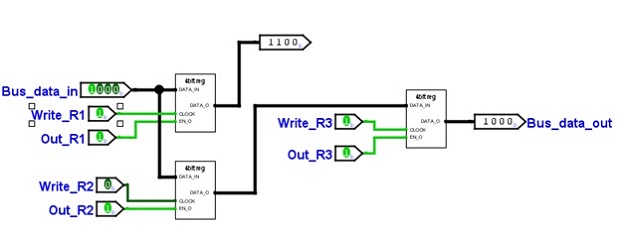

На главной схеме проекта построим схему, которая отражает задачу записи данных с выходов двух регистров в третий посредством общей шины, но предварительно выход первого регистра подключим к отдельному выходу для проверки работоспособности схемы. Промоделируем запись в регистры, а также чтение из них (рисунок 4.9).

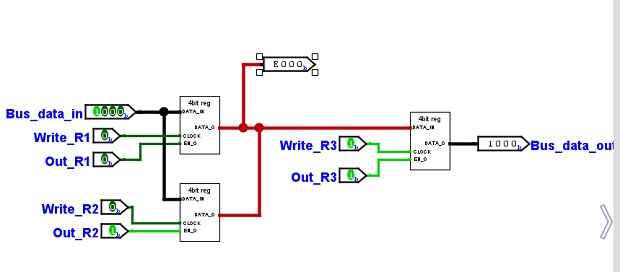

После объединения выходных шин двух регистров R1 и R2 система моделирования сформирует ошибку (рисунок 4.10).

Система предполагает, что при возникновении лог. "1" на одном из выходов регистра R2, при наличии управляющего сигнала на входе Out_R2, ток потечет помимо входа регистра R3 на соответствующий выход первого регистра, на котором присутствует сигнал лог. "0". Тем самым в цепи возникает короткое замыкание. Исходя из этого, регистры защелки не могут применять в качестве элементов управления выходом обычные вентили "И". Для объединения подобных регистров в схемотехнике применяются мультиплексоры либо шинные формирователи.

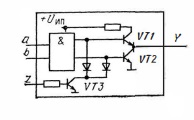

При проектировании регистров, если требуется добавить управление чтением данных, применяются специальные элементы с третьим состоянием (Z) - управляемые буферы. На этих же элементах строятся микросхемы, именуемые шинными формирователями [2].

Третье состояние элемента - состояние с высоким импедансом, то есть обратный ток, который может протекать в направлении данного элемента ничтожно мал и не приводит к выходу из строя схемы. На рисунке 4.11 приведена схема элемента с третьим состоянием. На примере данного элемента можно объяснить работу управляемых буферов. При лог. "1" на входе Z транзистор VT3 открыт, ток с выхода логического элемента стекает через диоды, тем самым закрывая транзисторы VT1 и VT2, разрывая связь логического элемента с выходом Y.

Изменим внутреннее устройство регистра, заменив вентили на управляемые буферы. В среде Logisim Evolution данные узлы находятся в блоке "Элементы", там имеется буфер как с прямым, так и с инверсным выходом. Измененная схема приведена на рисунке 4.12. Сохранив изменения в схеме регистра, вернемся на главную схему проекта и пронаблюдаем, что ошибка с подключением регистров в общую шину исчезла (рисунок 4.13).