Последовательностная логика. Регистры

Ярким примером применения управляемых буферов являются микроконтроллеры, в которых выводы могут назначаться входами/выходами или быть двунаправленными в зависимости от выполнения программы, меняя свое назначение в моменте ее работы.

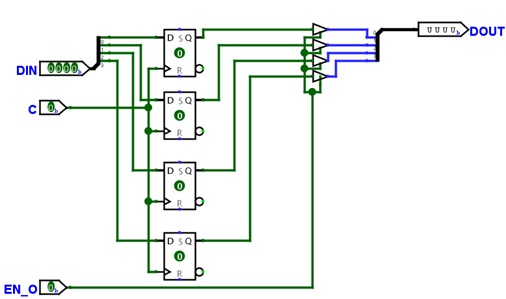

В среде Logisim Evolution смоделируем упрощенное управление выводом, на примере микроконтроллера Microchip. В данных микроконтроллерах имеется регистр TRIS (регистры именуются по именам портов TRISA, TRISB и т.д), управляющий направлением работы вывода, и регистр PORT (регистры именуются по именам портов PORTA, PORTB), который принимает или передает данные. Если в регистре TRIS какой-либо бит установлен в "1", то вывод работает на вход и данные с вывода поступают в соответствующий триггер регистра PORT и наоборот. На рисунке 4.14 приведена функциональная схема управления выводами микроконтроллера с применением управляющих буферов.

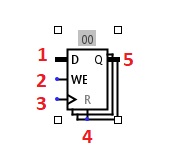

В среде Logisim Evolution регистр находится в разделе "Память" и представляет собой регистр - защелку (рисунок 4.15). Он имеет следующие входы/выходы: 1 - вход данных; 2 - управляющий сигнал разрешения записи WE - write enable; 3 - управляющий сигнал Clock; 4- R - управляющий сигнал сброса (reset); 5 - прямые выходы данных Q.

Запись в регистр может осуществляться при наличии сигнала WE (лог. "1") и сигнала Clock. В свойствах элемента можно выбрать различные варианты срабатывания регистра на данные сигналы: "Передний фронт", "Задний фронт", "Высокий уровень", "Низкий уровень". В свойстве "Биты данных" задается разрядность регистра (по умолчанию 8).

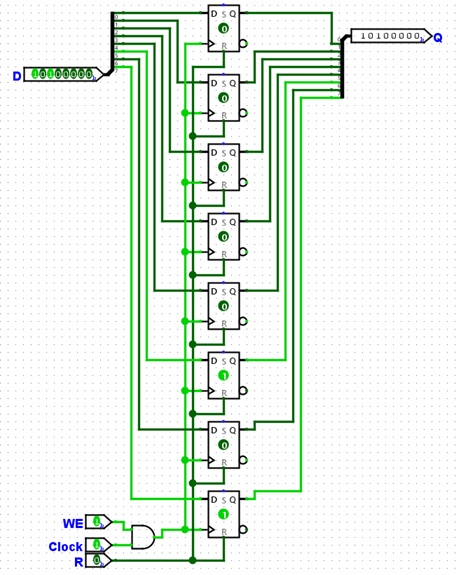

На рисунке 4.16 приведена эквивалентная функциональная схема данного регистра, срабатывающая по переднему фронту сигнала Clock.

В листинге 4.1 приведен код на языке Verilog HDL, описывающий представленный на рисунке 4.16 регистр.

module parallel_reg (

input wire [7:0] D, // Параллельный вход данных

input wire Clock, //Синхросигнал

input wire R, // Асинхронный сброс

input wire WE, // Вход управления записи

output reg [7:0] Q // Выходные данные

);

// Процесс, описывающий поведение регистра

always @(posedge Clock or posedge R) begin

if (R) begin

Q <= 8'b0; // Асинхронный сброс: выход в 0

end else begin

if (WE) begin

Q <= D; // Запись данных при фронте Clock и наличии WE

end

end

end

endmodule

Листинг

4.1.

В ядре процессора регистры - параллельные. Они мультиплексируются в шины, а адресуются блоком управления (дешифратором или демультиплексором).

В практической работе 3 необходимо выполнить проектирование регистрового банка памяти.

Сдвиговые регистры

Сдвиговый регистр - это регистр, содержимое которого при подаче управляющего сигнала "сдвиг" сдвигается в сторону старших либо в сторону младших разрядов. Сдвиговые регистры применяются для преобразования последовательного кода в параллельный и наоборот. Сдвиговые регистры применяются при организации передачи данных. На рисунке 4.17 показан пример последовательно-параллельного регистра со сдвигом в сторону старших разрядов (вправо), реализованный в среде Logisim Evolution. На функциональной схеме входы имеют следующее назначение: