Последовательностная логика. Регистры

После создания графического обозначения элемента ANDOR необходимо вернуться на главную схему main, которую рекомендуется переименовать в SN7495. На ней разместить элементы ANDOR.

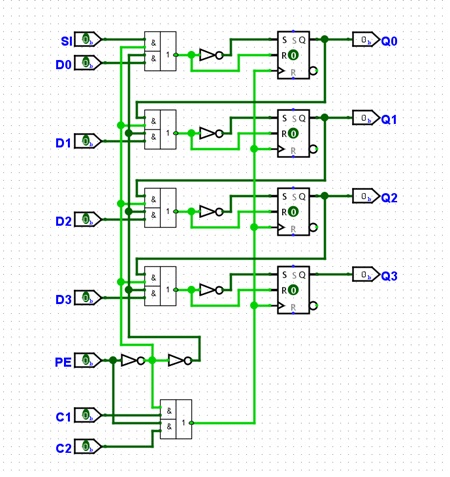

Разместим на поле схемы четыре триггера SR. Триггеры разместим вертикально: верхний младший, нижний старший. Напротив каждого триггера разместим блок ANDOR. Входы S каждого триггера подключим через инвертор к выходу ANDOR. Входы R подключим напрямую. Прямые выходы Q каждого триггера подключим к верхним входам элемента ANDOR. К выходам Q каждого триггера подключим элемент выход. Меткам зададим имена Q0-Q4. Второй вход верхних блоков "&" элементов ANDOR объединим инвертором и подключим к входу РЕ. Вход PE имеет повторитель сигнала, реализованный на инверторах. Если первый инвертор обеспечивает последовательную загрузку данных при логическом 0 на данном входе, то с выхода второго инвертора сигнал поступает на объединённый вход нижнего блока "&" элементов ANDOR, тем самым разрешает запись данных в триггеры с входов D0-D4. Данные входы подключены к вторым входам нижних блоков "&" элементов ANDOR. Входы синхронизации триггеров управляются также блоком ANDOR. В зависимости от уровня сигнала PE работает либо верхний, либо нижний элемент блока ANDOR, обеспечивая разрешение записи в регистр с входов D0-D3, либо осуществляя последовательный сдвиг. Функциональная схема приведена на рисунке 4.34.

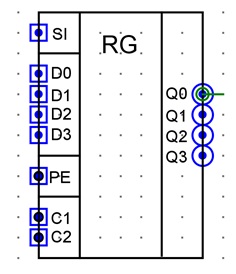

По окончании моделировании схемы регистра следует перейти в редактор внешнего вида и оформить УГО как показано на рисунке 4.35.

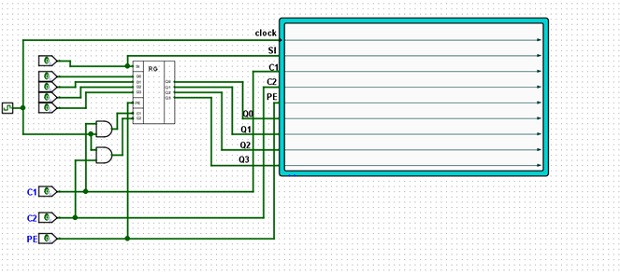

Далее добавим новую схему, которую назовем TEST. Данную схему назначим главной, выбрав ее в иерархическом списке схем. Кликнув правой кнопкой мыши по имени схемы, вызовем ниспадающее меню и выберем "Сделать главной схемой".

Далее реализуем схему моделирования, приведенную на рисунке 4.36. Результат моделирования должен совпадать с таблицей истинности, приведенной на рисунке 4.30.

Самостоятельно

- Добавить в проектируемый регистр инверсный (управляющий сигнал лог. "0") вход управления OE (Output Enable), разрешающий выдавать информацию из регистра.

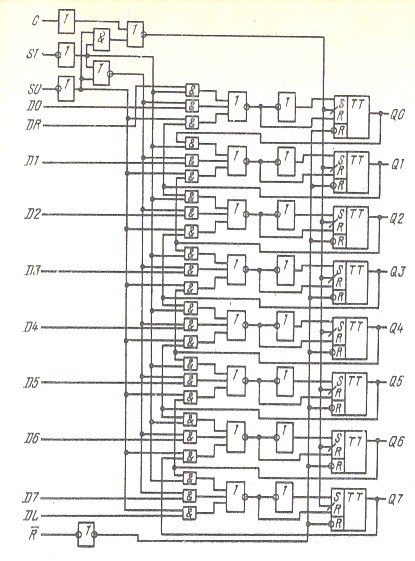

- В среде Logisim Evolution воспроизвести схему представленную, на рисунке 4.37. Сформировать тестовое окружение для проверки ее работы. Построив схему, реализовать таблицу истинности работы регистра, приведенного на схеме. В среде Quartus на языке VerilogHDL создать описание данного регистра, разработать файл тестирования и выполнить симуляцию его работы.

Практическая работа 4. "Проектирование банка памяти на параллельных регистрах"

Реализовать регистровую память на параллельных регистрах в среде Logisim Evolution с заданными по вариантам параметрами. На рисунке 4.38 приведен пример организации регистровой памяти 4х8. Входы данных D регистров объединены. Выходы данных Q мультиплексируются четырехпортовым восьмиразрядным мультиплексором D6. Адресация записи в регистры памяти осуществляется дешифратором D1, выходы которого подключаются к входам управления записи WE регистров D2-D5. Сигнал WE управляет записью в регистры. При уровне лог. "1" осуществляется запись. Данные регистров снимаются с соответствующего регистра через мультиплексор D6. Адрес для чтения из регистровой памяти задается на шине ADDRESS