Арифметико-логическое устройство

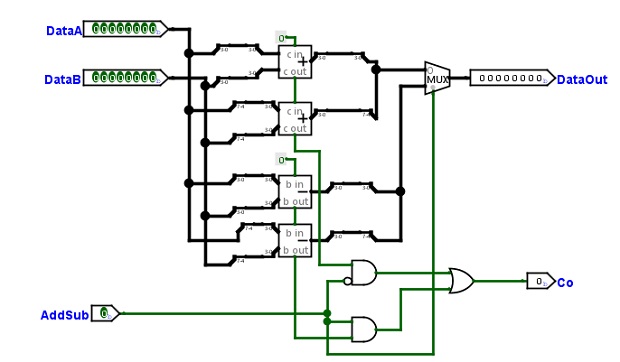

На рисунке 6.17 приведена функциональная схема для описываемого арифметического узла АЛУ. Вход AddSub является управляющим сигналом осуществляющим, как было сказано в начале раздела коммутацию комбинационных схем посредством мультиплексора и управлением выходом Со - совмещенным выходом переполнения / заема для операций блока. При лог. "0 " на входе AddSub арифметический блок выполняет сложение. При лог. "1 " операцию вычитания. Сигнал лог. "1 " на входе AddSub совместно с возникающем сигналом переполнения Со, может быть анализирован в блоке управления при выполнении микропрограммы.

Реализация блока АЛУ для проектируемого в рамках курса процессора RISC-V будет рассмотрена в практической работе.

Лабораторная работа 5. "Проектирование матричного умножителя "

Цель лабораторной работы закрепить навыки работы с элементами арифметики в двоичном коде. Получить навыки работы с инструментом проверки работы схемы "Тестовый вектор ".

Существует множество алгоритмов для выполнения операций умножения. Данная операция требовательна к ресурсам центрального процессора, поэтому является одной из сложных с точки зрения быстродействия. В литературе [1] подробно рассмотрены варианты организации алгоритмов и схем для операций умножения, а также подобно описаны различные механизмы операции деления. Для повышения быстродействия применяют матричные умножители. Данные умножители не лишены недостатков, таких как площадь, занимаемая ими на кристалле микросхемы, растущая с ростом разрядности слов.

Для умножения без знака рассмотрим умножитель Брауна.

Умножитель Брауна эффективен в контексте использования избыточных битов. Каждый из промежуточных результатов сохраняет информацию, позволяя избежать необходимости использования дополнительных стадий суммирования.

В основе лежит таблица частичных произведений, которая строится на основе входных двоичных чисел. Это позволяет сократить общее количество необходимых для сложения и умножения операций.

Принцип работы:

На вход поступают числа A и B, которые необходимо перемножить. Число A имеет n бит, а число B - m бит.

Умножение осуществляется через генерацию частичных произведений. Каждая из строк частичных произведений формируется логическим умножением одного бита из B на все биты A.

Матричная структура обеспечивается следующим образом, например  и

и  , то частные произведения формируются следующим образом:

, то частные произведения формируются следующим образом:

- первая строка:

;

; - вторая строка:

;

; - и так далее пока не будут сгенерированы все строки.

После того как все частичные произведения созданы, они складываются. Это сложение происходит в несколько этапов с учетом переноса.

Для оптимизации данного умножителя могут использоваться такие методы, как параллельное сложение и специфические схемы переноса.

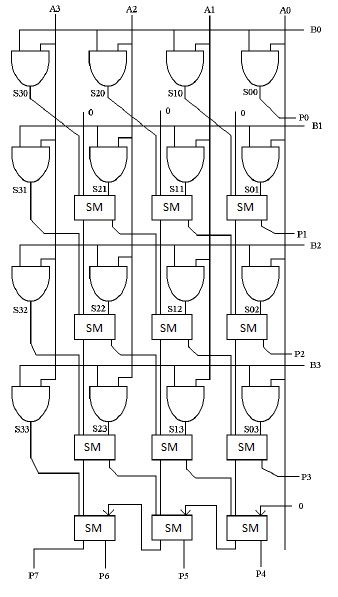

На рисунке 6.18 приведена функциональная схема для данного умножителя.

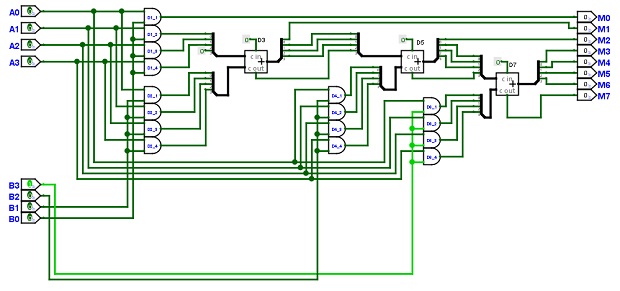

В среде Logisim Evolution создать новый файл сохранить его под именем MUL. Данный матричный умножитель производит операцию умножения для двух четырехразрядных слов А и B.

Необходимо построить схему, приведенную на рисунке 6.19. На четырехразрядных сумматорах D3,D5,D7 реализуется схема сложения частных произведения. На конъюнкторах D1_1 - D1_4 реализуется получение частного произведения множимого слова A0-A3 на бит B0 множителя B0-B3, на коъюнкторах D2_1-D2_4 соответственно происходит получение частного произведения А0-А3 на бит B1, и так далее. Входы переносов из младших разрядов сумматоров необходимо подключить к константе лог. "0 ". Вход старшего разряда сумматора D3 также подключить к константе лог. "0 ". Младший результат произведения сразу же будет получен на выходе элемента D1_1. Результаты сложения частных поступают на входы (А) следующих сумматоров со смещением на один разряд в сторону старших (как видно из схемы), причем старшим разрядом является выход переноса из младшего сумматора. Младшие выходы результатов сложения являются выходами результата произведения. С выходов сумматора D7 снимаются старшие разряды, восьмиразрядного результата произведения М0-M7. Старший разряд M7 снимается с выхода переноса сумматора D7.