Арифметико-логическое устройство

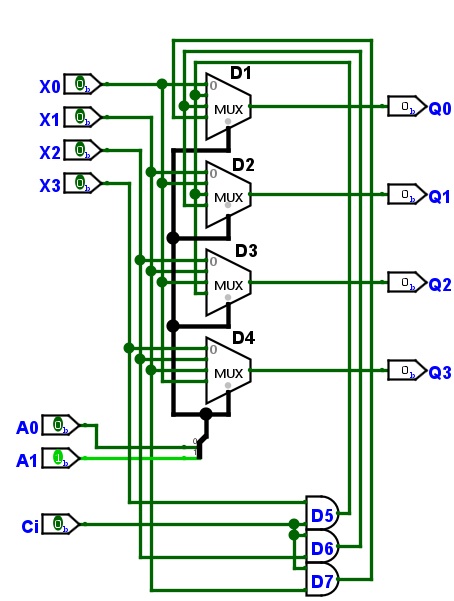

В листинге 6.3 приведен пример реализации поведенческого описания схемы логического сдвига, показанного на рисунке 6.13 на языке Verilog HDL.

module logi_shift (X, A, Q);//определение модуля и имен сигналов input [3:0] X;//вход свдигаемого слова input [1:0] A;// селектор управляющий сдвигом output reg [3:0] Q;//шина данных выходного слова always @(X or A) // анализируем изменения сигналов на входе данных или //селектора begin case (A)//анализируем состояние селектор 2'b00: Q = X;// входные данные поступают на выход без сдвига 2'b01: Q = X<<1;// сдвиг на один бит влево 2'b10: Q = X <<2;//сдвиг на два бита влево default: Q = X <<3;//сдвиг на три бита влево endcase end endmoduleЛистинг 6.3.

На рисунке 6.15 представлен данный цифровой блок на уровне RTL.

В среде Logisim Evolution в разделе "Арифметика " находятся узлы, которые будут применятся для проектирования АЛУ процессора.

В таблице 6.3 приведено условно-графическое обозначение, применяемых элементов и назначение сигналов.

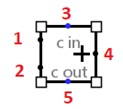

| Наименование блока (арифметических операций) | Условно-графическое обозначение | Назначение сигналов |

|---|---|---|

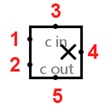

| Сумматор |

1 -вход первого слагаемого (шина данных); 2 - вход второго слагаемого (шина данных); 3 - вход переноса из младшего сумматора; 4 - выход результата суммы (шина данных); 5 - выход переполнения (в старший сумматор). |

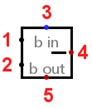

|

| Субтрактор (Вычитатель) |

1 - вход уменьшаемого (шина данных); 2 - вход вычитаемого (шина данных); 4 - выход результата разности (шина данных); 5 - выход займа (в старший вычитатель). |

|

| Умножитель (Множитель) |

1 - вход множимого (шина данных); 2 - вход множителя (шина данных); 4 - выход результата произведения (шина данных); 5 - выход переполнения (в старший множитель). |

|

| Делитель |

1 - вход делимого (шина данных); 2 - вход делителя (шина данных); 4 - выход частного (шина данных); 5 - выход остатка (в старший делитель). |

|

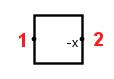

| Преобразователь в дополнительный код (отрицатель) |

1 - входная шина данных; 2 - выходная шина данных в виде дополнительного кода. |

|

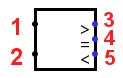

| Компаратор |

1 - вход первого слова А (шина данных); 2 - вход второго слова В (шина данных); 3 - выходной сигнал, активен если слово А>B; 4 - выходной сигнал, активен если слово А=B; 5 - выходной сигнал, активен если слово А<B; |

|

| Схема сдвига (сдвигатель) |

1 - вход сдвигаемого слова (шина данных); 2 - вход управления (шина данных), указывающего на количество сдвигаемых бит; 3 - выход (шина данных) сдвига. Важно! В свойстве "Тип сдвига " задается направление сдвига "Логический правый ", "Логический левый ", "Арифметический правый ", "Циклический левый ". |

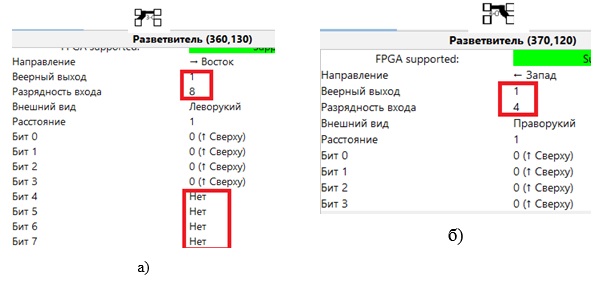

В качестве демонстрации организации каскадного включения сумматоров и вычитателей, имеющихся в среде Logisim, а также организации АЛУ, собрано тестовое арифметическое устройство для сложения и вычитания двух восьмиразрядных слов. Узлы в проектируемом устройстве выбраны четырехразрядные. Разделение входных шин, сборка результата выполняется при помощи инструмента разветвителя. На рисунке 6.16а показаны настройки разветвителя восьмиразрядной шины из которой извлекаются младшие 4 бит. На рисунке 6.16б показана настройка четырехразрядной шины приемника.