Основы работы в средах Logisim и Quartus Prime Lite

2. Представление целых и действительных чисел в Verilog

Для представления целых чисел применяется следующий формат записи: size'base value, где size - размер, определяющий систему счисления, в которой представлено число, base - система счисления числа, value - непосредственное значение.

Для обозначения базы применяются следующие символы:

- 'd или 'D - десятичные числа;

- 'b или 'B - двоичные числа;

- 'o или 'O - восьмеричные числа;

- 'h или 'H - шестнадцатеричные числа;

Примеры:

4'b1010 - двоичное четырёхразрядное число (в десятичной системе 10);

6'o71 - шестиразрядное восьмеричное число;

8'd127 - восьмиразрядное десятичное число 127;

127 - десятичное число (по умолчанию).

Для представления действительных чисел в Verilog применяется запись либо c десятичной точкой, либо в экспоненциальном виде. Запись с точкой имеет вид: value_i.value_f, где: value_i - целая часть, value_f - дробная часть

Примеры:

1.8 3.8e10 // e или E для равно2.1e-9// 2,1*

3. Выражения

Выражения и операции на языке Verilog, применяющие примитивы относятся к следующим видам:

- логические операции, например, a && b - логическое "И";

- арифметические операции, например, a + b - это сложение двух чисел одинаковой разрядности с переполнением;

- побитные операции, например, a & b - это побитное "И" двух битовых массивов одинаковой длины;

- отношения, например, a<b возвращает логическую 1, если число, двоичная запись которого есть a, меньше такового для b, и логический 0 иначе.

- конкатенации, например, {a, b} - битовый массив, составленный из a и b;

- редукции, например, &a - имеет логическую 1, если все биты a равны лог "1", и логический 0 иначе;

- условия,например, cond ? a : b работает как в C++. cond должно иметь логическое значение, a и b должны иметь одинаковое число бит.

В таблице 1.3 приведены операции языка Verilog для построения выражений.

| Побитные операторы | |

| ~ | инверсия |

| & | побитное "И" |

| | | побитное "ИЛИ" |

| ^ | побитное "Исключающее ИЛИ" |

| ~^ или ^~ | побитное "Исключающее ИЛИ НЕ" |

| Логические операторы | |

| ! | логическое "НЕ" |

| && AND | логическое "И" |

| || OR | логическое "ИЛИ" |

| Редукция | |

| & | редуцированное "И" |

| ~& | редуцированное "НЕ-И" |

| | | редуцированное "ИЛИ" |

| ~| | редуцированное "НЕ-ИЛИ" |

| ^ | редуцированное "Исключающее ИЛИ" |

| ~^ или ^~ | редуцированное "Исключающее ИЛИ НЕ" |

| Арифметические операторы | |

| + | сложение |

| - | вычитание |

| * | умножение |

| / | деление |

| Отношение | |

| > | больше |

| < | меньше |

| >= | больше либо равно |

| <= | меньше либо равно |

| = = | логическое равенство |

| != | логическое неравно |

| = = = | 4 state логическое равенство |

| != = | 4 state логическое неравно |

| Операции сдвига | |

| >> | логический сдвиг вправо |

| << | логический сдвиг влево |

| >>> | арифметический сдвиг вправо |

| <<< | арифметический сдвиг влево |

| Разное | |

| { , } | склеивание |

| {n{m}} | копирует m значение n раз |

| ? : | условие |

В листинге 1.3 приведен пример организации комбинационной схемы сравнения, использующей операторы отношения.

module comparator ( input [7:0] A, B, output O_EQ, O_NE, O_BR, O_MR, O_BOL, O_MEN); assign O_EQ = A == B; assign O_NE = A != B; assign O_BR = A >= B; assign O_MR = A <= B; assign O_BOL = A >B; assign O_MEN = A < B; endmoduleЛистинг 1.3.

4. Оператор непрерывного присваивания assign

Оператор assign в Verilog предназначен для описания непрерывных присвоений в структуре цифровых схем. Этот оператор используется для связывания значений между сигналами и переменными.

Назначение оператора assign:

- Позволяет задавать непрерывные присвоения между проводами и переменными. Это означает, что результат выражения всегда будет обновляться автоматически при изменении входных сигналов.

- С помощью assign можно описываются логические цепи и комбинационные схемы.

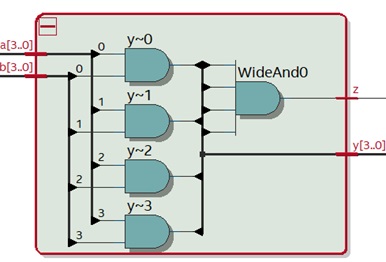

В листинге 1.4 дается пример применения оператора assign. На рисунке 1.14 можно наблюдать результат на уровне RTL.

module logic_operators ( input [3:0] a, b, // объявление входных векторных портов output [3:0] y, // объявление выходного векторного порта output z); assign y = a & b; // побитная операция " И" над входами assign z = & y; // редукция, объединение выходов y через операцию "И" и получение выхода //Z endmoduleЛистинг 1.4.

Возможно присваивание при объявлении, например, wire [2:0] z = x + y;.