|

Здравствуйте! Прошел курс, а где экзамен? Как сертификат получить? Без экзамена? |

Основы работы в средах Logisim и Quartus Prime Lite

1.1. Основы проектирования и верификации модулей

Для начала решения проблемно-ориентированных задач, следует остановиться на важнейшем разделе любого проекта - определение этапов выполнения проекта:

- Постановка задачи и формирование технического задания.

- Формализация задания и выполнение математической модели.

- Ввод описания проекта (выбор инструментов и способа описания, непосредственно описание проекта);

- Построение моделирующего алгоритма

- Создание тестового окружения и верификация проекта.

- Отладка и устранение выявленных ошибок, выполнение повторных тестов.

- Анализ результатов и их документирование.

- Передача результатов заказчику.

Сформируем следующую задачу: необходимо разработать и реализовать схему с тремя входами для мажоритарного контроля, используя язык описания аппаратуры Verilog. Схема должна сравнивать три входа и выдавать сигнал, равный лог. "1" если два или более входов равны лог. "1".

Уточним требования к интерфейсу проектируемой схемы и уровням сигналов реакции:

-

Входные сигналы:

- a: первый вход (сигнал 1 бит);

- b: второй вход (сигнал 1 бит);

- c: третий вход (сигнал 1 бит);

- Выходной сигнал - y, на котором установится лог. "1" если как минимум на двух входах будет присутствовать лог "1".

Выполним математическое моделирование. Для этого сформируем по условиям таблицу истинности (таблица 1.2).

| п/п | Входы | Выход | ||

|---|---|---|---|---|

| A | b | c | y | |

| 1 | 0 | 0 | 0 | 0 |

| 2 | 0 | 0 | 1 | 0 |

| 3 | 0 | 1 | 0 | 0 |

| 4 | 0 | 1 | 1 | 1 |

| 5 | 1 | 0 | 0 | 0 |

| 6 | 1 | 0 | 1 | 1 |

| 7 | 1 | 1 | 0 | 1 |

| 8 | 1 | 1 | 1 | 1 |

Проведем анализ таблицы 1.2 истинности и определим строки, в которых комбинация входных сигналов обеспечит лог. "1" на выходе. В данном случае это 4, 6,7,8 строки. Выпишем их:

- (a=1,b=1,c=0);

- (a=1,b=0,c=1);

- (a=0,b=1,c=1);

- (a=1,b=1,c=1);

Сформируем СКНФ из данных:

![y=a*b*\bar c+a*\bar b*c+]bar a*b*c+a*b*c](/sites/default/files/tex_cache/7bced551df4792f87278c2f41e6b0ab2.png)

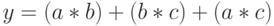

После преобразований формула примет вид:

Введем проект на заявленном языке Verilog. Определим имя модуля как major, тип сигнала интерфейса - wire. Имена сигналов были заданы в условии.

Используя процедурный оператор assign, введем функцию, описанную выше на языке Verilog как показано в листинге 1.2.

module major ( // начало модуля

input wire a, // первый вход

input wire b, // второй вход

input wire c, // третий вход

output wire y // выход мажоритарного значения

);

assign y = (a & b) | (b & c) | (c & a); // реализуемая функция

endmodule // окончание модуля

Листинг

1.2.

1.1.1. Верификация

При создании цифровых устройств одним из сложных и самых трудоемких этапов является процесс верификации. Данный этап может отвлекать от 50 до 80% всего времени выполнения проекта.

Верификация - это процесс установления соответствия созданного устройства, техническим условиям спецификации из технического задания.

В рамках верификации выполняются различные тесты, причем могут вноситься изменения в конечную спецификацию устройства.

В рамках выполнения верификации одним из этапов является процедура функциональной верификации - проверка на наличие ошибок в проекте. Для выполнения функциональной верификации применим инструменты симуляции работы схемы.

Так как разработанный выше модуль является достаточно простым, то его функциональная верификация будет несложной - сверка таблицы истинности и временной диаграммы работы. Но наша задача получить первичное представление о верификации и методах ее проведения.

Для проверки разработанного кода перенесем его в среду проектирования Intel Quartus.

- Создадим проект с именем major.

- Создадим новый файл Verilog HDL и введем код из листинга, сохраним файл с именем major.v.

- Выполним компиляцию проекта в основном меню среды "Processing" - "Start Compilation"

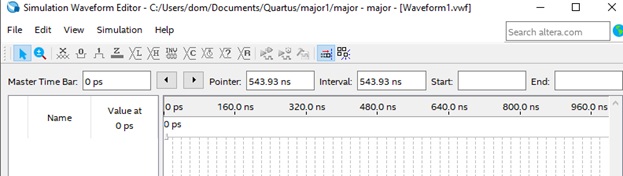

- Далее воспользуемся инструментом для ввода тестовых векторов, отслеживания изменения внутренних линий и состояния выходных портов - Waveform Editor. Для этого пройдя в меню "File" - "New", выберем в разделе "Verification/Debugging Files" пункт "University Program VWF".

-

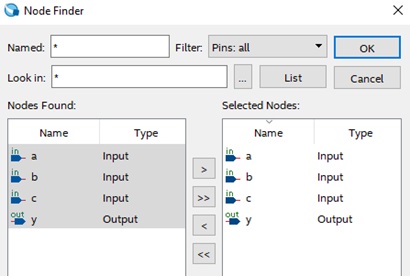

В открывшейся форме (рисунок 1.1), добавим входы и выход модуля через меню "Edit" - "Insert" - "Insert Node or Bus" (рисунок 1.2). Нажав на кнопку "Node Finder", перейдем на форму выбора сигналов. Так как мы выбираем все сигналы, нажмем на кнопку "List". Исследуемые сигналы (все) переместим в поле "Selected Nodes", нажав на кнопку >> (рисунок 1.3).

-

Необходимо исключить один из параметров работы симулятора - noopt. Для этого перейти в меню "Simulation" - "Simulation Settings".

В открывшемся окне, найдем данный параметр и удалим (рисунок 1.4).

- Далее выполняется создание тестовых уровней сигналов. Для этого левой кнопкой мыши выбирается временной отрезок (одна или несколько клеток). После выбора он заливается синим цветом. Далее необходимо в меню инструментов выбрать уровень сигнала, в данном случае выбрать лог. "1" -.

- Исходя из таблицы истинности формируем тестовые сигналы как показано на рисунке 1.5.

- Далее выполняется функциональная симуляция через меню "Simulation" - "Run Functional Simulation". Полученную диаграмму (рисунок 1.6) необходимо сверить с заданными в техническом задании условиями, а также с таблицей истинности.