Основы работы в средах Logisim и Quartus Prime Lite

Более совершенные методы верификации подразумевают применение тестирующего оборудования или отладочного модуля, именуемого testbench. Testbench генерирует набор сигналов для проектируемого устройства, а затем принимает их для последующего анализа.

Стратегия работы с тестовым окружением - поочередная подача восьми возможных комбинаций на входы a,b,c

Для создания testbench необходимо рассмотреть основы синтаксиса данных файлов.

Первая строка кода testbench может содержать директиву масштаба модельного времени, определяющая значение залежек модели, которая начинается с обратной кавычки: `timescale. С этой директивой указываются временные параметры: N1 - определяет единицы времени задержки сигналов, следующих за символом #; N2 - точность расчета.

Оба параметра указываются в наносекундах или пикосекундах и могут принимать значения только 1, 10 или 100. По умолчанию назначаются ps.

Пример: `timescale 1ns/1ns

В следующей строке тестового модуля указывается ключевое слово module и имя модуля с обязательной приставкой tb, указывающей на то, что это тестовый модуль проекта.

Так как это тестовый модуль, то он не имеет портов. В него вставляется тестируемый модуль и входы/ выходы тестируемого модуля взаимодействуют с переменными типа reg и wire.

Например, для тестируемого модуля будет применено следующее объявление:

reg a; reg b; reg c; wire y;

Следующей частью кода является инстанцирование тестируемого модуля в тестовый модуль. При этом в списке портов устанавливается соответствие между портами тестового и тестируемого модулей. Модуль testbench в общем случае, может иметь отличные от тестируемого имена входов/выходов.

После имени тестируемого модуля должен быть указан тип подсистемы, которая тестируется:

- DUT (device under test), обозначает любое устройство или компонент, который тестируется. Это может быть целая система или отдельный модуль, в зависимости от уровня верификации.

- UUT (unit under test), это подмножество DUT, обычно подчеркивающее конкретный модуль или блок, который тестируется в рамках более крупного устройства или системы.

Пример инстанцирования для рассматриваемого примера:

major uut (

.a(a),

.b(b),

.c(c)

Далее с помощью конструкций, определяемых ключевыми словами initial begin…end выполняется моделирование.

Конструкции содержат описания начальных значений и дальнейшего поведения входных сигналов во времени. Блок initial задает симулятору точку, с которой начинается работа. Следует отметить, что тестовый модуль без блока initial не работает.

Следующим этапом указываются варианты поведения сигналов и указание временных единиц (задержки) для их смены.

Также можно применять команды для вывода информации во время симуляции:

- $display, выводит информацию только в момент вызова;

- $monitor, выводит информацию каждый раз при изменении отслеживаемых переменных.

Пример: $monitor("a=%b, b=%b, c=%b, y=%b", $time, a, b, c, y);

Далее указывается одна из конструкций системной директивы $finish, которая завершает процесс моделирования. И наконец, ключевое слово endmodule указывает на окончание описания тестового модуля.

В листинге 1.3 приведен исходный код тестового модуля tb_major

`timescale 1ns/1ns

module tb_major;

reg a;

reg b;

reg c;

wire y;

major uut (

.a(a),

.b(b),

.c(c),

.y(y)

);

initial begin

$monitor("a=%b, b=%b, c=%b, y=%b", $time, a, b, c, y);

a = 0; b = 0; c = 0;//y=0

#10;

a = 0; b = 0; c = 1;//y=0

#10;

a = 0; b = 1; c = 0;//y=0

#10;

a = 0; b = 1; c = 1;//y=1

#10;

a = 1; b = 0; c = 0;//y=0

#10;

a = 1; b = 0; c = 1;//y=1

#10;

a = 1; b = 1; c = 0;//y=1

#10;

a = 1; b = 1; c = 1;//y=1

#10;

$finish;

end

endmodule

Листинг

1.3.

Для реализации верификации с использованием созданного тестового модуля необходимо выполнить ряд манипуляций с проектом.

- Файл testbench сохранить в каталоге проекта под именем tb_major.v;

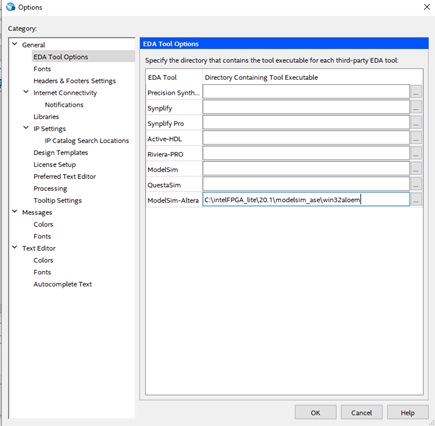

- Перейти в меню "Tools" - "Options". В открывшемся окне, перейти на вкладку EDA Tool Options (рисунок 1.7). В поле Modelsim-Altera указать путь к каталогу симулятора (по умолчанию: C:\intelFPGA_lite\20.1\modelsim_ase\win32aloem). Нажать кнопку ОК.

-

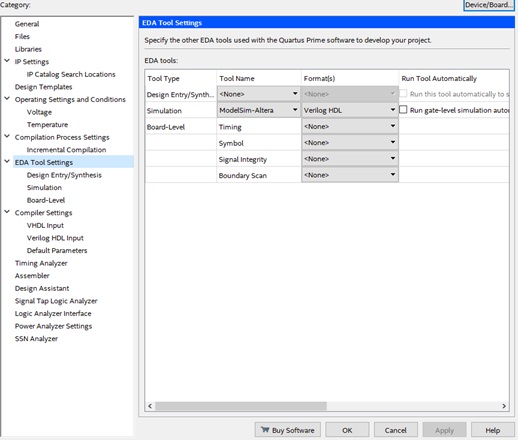

Перейти в меню "Assigments" - "Settings". В открывшемся окне, перейти в раздел "EDA Tool Settings". В строке "Simulation" для столбца "Tool Name" выбрать Modelsim-Altera. В столбце "Format(s) " выбрать Verilog HDL (рисунок 1.8). Нажать кнопки Apply и OK.

-

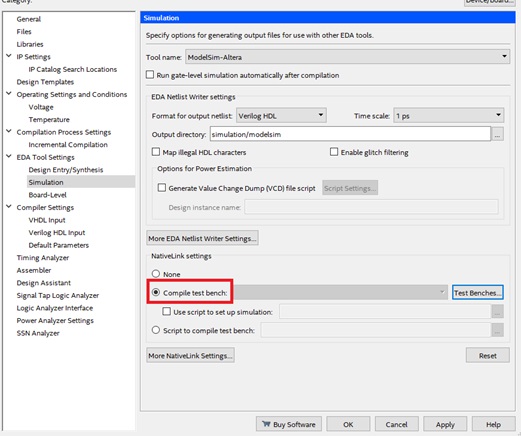

Далее в меню пройти в меню "Assigments" - "Settings". В открывшемся окне, перейти в подраздел "Simulation" раздела "EDA Tool Settings". В окне настроек установить метку "Compile test bench" (рисунок 1.9).

-

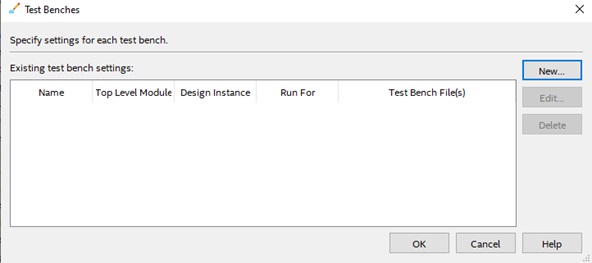

Нажать кнопку Test Benches. В новом окне (рисунок 1.10), нажать накнопку New.

-

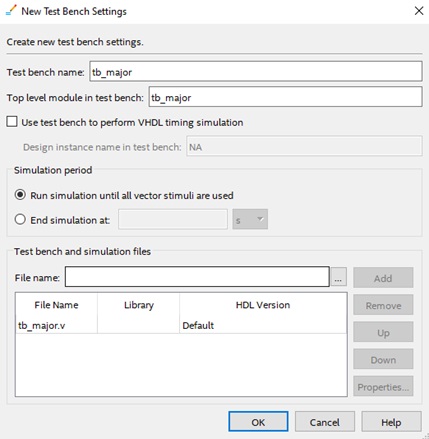

В диалоговом окне, приведенном на рисунке 1.11, в поле Test bench name ввести tb_major. Далее добавить файл, нажав на кнопку "… " поля "File name". Выбрать файл и нажать кнопку Add, затем кнопку ОК.

-

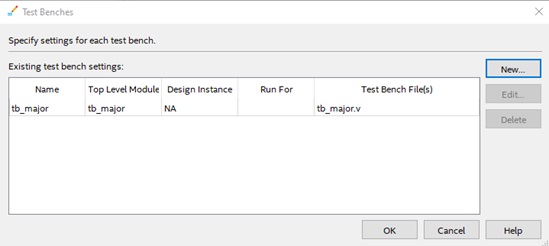

Вернувшись в окно Test Benches, убедиться, что файл добавлен (рисунок 1.12). Далее нажать OK.

- В окне "Settings" нажать кнопки Apply и OK.

- Выполнить компиляцию проекта. В случае успешной компиляции запустить симуляцию проекта ("Tools" - "Run Simulation Tool" - "RTL Simulation"). Откроется инструмент ModelSim.

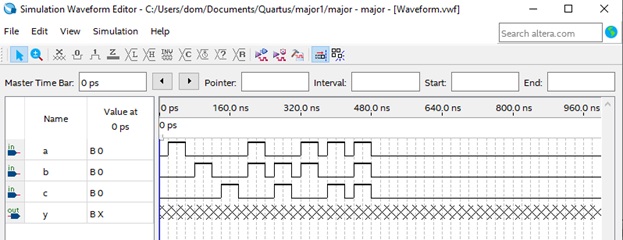

- Результат симуляции отобразится в виде диаграммы на панели Wave (рисунок 1.13). Текстовые сообщения выводятся в панели Transcript.

- Убедившись в верности отображаемых данных, можно окончить работу симуляции и завершить работу программы ModelSim.

Необходимо отметить, что качественный testbench должен содержать код самопроверки, то есть операторы, отслеживающие возникновение ошибки в ходе работы.