Схемотехническая реализация элементов вычислительной техники

Комбинационные схемы

Мы выше рассмотрели, что существует набор элементарных логических функций, с помощью которого можно построить любую другую логическую функцию. Обычно для каждой элементарной логической функции (а иногда и для суперпозиции таких функций) промышленность выпускает набор логических элементов, объединенных общими электрическими, конструктивными и технологическими параметрами и использующих одинаковый тип межэлементных связей, который позволяет создать некоторую схему, выполняющую ту или иную логическую функцию.

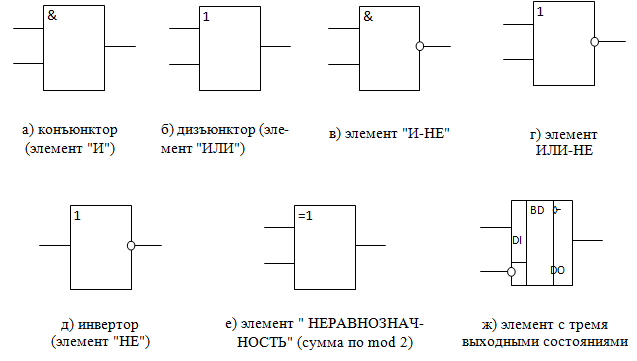

Условно-графические обозначения (УГО) некоторых логических элементов представлены на Рис. 5.1.

УГО элемента представляет собой прямоугольник, к которому слева подходят входные сигналы, а справа выходят выходные. Внутри прямоугольника ставится условное обозначение выполняемой элементом логической функции. Если значение выходного сигнала принимает инверсное значение по отношению к обозначенной внутри элемента функции, то данный выход обозначается на УГО элемента кружком (рис.1,в – 1,д). Аналогично, если активным уровнем входного сигнала является логический "0", то данный вход обозначается кружком (вход E элемента 1,ж).

Если элемент выполняет сложную функцию, имеет несколько функционально различных групп входов и выходов, то входы и выходы отделяются от основного поля УГО вертикальными линиями. Внутри каждого из получившихся полей функционально различные группы входов и выходов отделяются друг от друга горизонтальными линиями. На рис.1,ж показан элемент, выход которого может находиться в одном из трех состояний: логический "0", логическая "1", состояние высокого сопротивления. В состоянии высокого сопротивления выход элемента отключается от входов всех других элементов, с которыми он связан. Вход E (enable) этого элемента управляет состоянием его выхода. Так как на условно-графическом обозначении этот вход отмечен кружком, то отсюда следует, что функция разрешения передачи двоичного сигнала с входа на выход элемента выполняется при состоянии логического "0" на входе разрешения E. Если на вход E подан сигнал логической "1", то выход элемента находится в отключенном (так называемом "третьем") состоянии.

Каждый логический элемент – это электронно-техническое изделие (Рис. 5.2). В этих схемах все транзисторы работают в ключевом режиме. Это означает, что при подаче сигнала высокого уровня на базу транзистора, его сопротивление становится пренебрежимо малым, то есть транзистор как бы "стягивается в точку". При низком потенциале на базе транзистора сопротивление между коллектором и эмиттером становится чрезвычайно большим, что фактически означает разрыв цепи.

Рассмотрим это на примере работы инвертора (рис.5.2,а). Если сигнал X имеет высокий потенциал, то ключ, реализованный на транзисторе, замкнут, и потенциал точки Y низкий. В противном случае связь между точкой Y и "землей" разорвана, и сигнал Y имеет высокий уровень, что и обеспечивает реализацию логической функции "отрицание".

Для элемента "И-НЕ" сигнал в точке Yбудет иметь низкий уровень (НУ) лишь тогда, когда оба сигнала X1 и X2 имеют высокий уровень (ВУ). Работа этого элемента описывается Табл. 5.1.

Если принять, как это делается в наиболее распространенных сериях логических элементов, высокий уровень сигнала за логическую"1", а низкий уровень – за логический "0", то получим таблицу истинности данного элемента (Табл. 5.2).

Эта таблица соответствует логической функции "И-НЕ".

В то же время, принимая высокий уровень сигнала за логический "0", а низкий уровень – за логическую "1", получим следующую таблицу истинности (Табл. 5.3).

Эта таблица соответствует уже функции "ИЛИ-НЕ".

Таким образом, кодирование сигналов в системе логических элементов может влиять на выполняемую им логическую функцию. В дальнейшем будем полагать кодировку сигналов, принятую для Табл. 5.2.

Для элемента "ИЛИ-НЕ" (см. Рис. 5.2) сигнал в точке Y будет иметь высокий уровень лишь тогда, когда оба сигнала X1 и X2 имеют низкий уровень. Работа этого элемента описывается Табл. 5.4, а его таблица истинности при сделанных предположениях о кодировке сигнала – Табл. 5.5. Эта таблица соответствует логической функции "ИЛИ-НЕ".