Проектирование блока управления

Далее необходимо разработать схему управления АЛУ. При проектировании блока АЛУ было создано 4-х разрядное поле микроопераций. Если провести сравнение с форматом инструкций для арифметико-логического устройства, то можно определить, что микрооперация определяется как состояние пятого бита поля funct 7 и кода в поле funct3. Из анализа инструкций можно сделать вывод, что funct 7 составная часть поля микрокоманды операций АЛУ - старший бит.

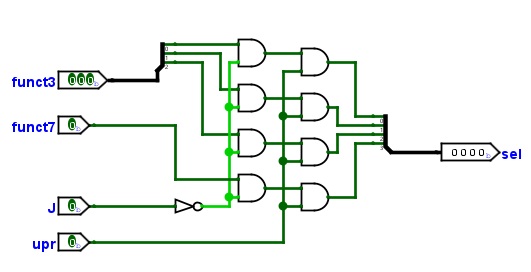

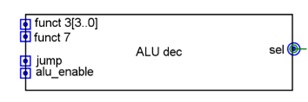

Создадим новую схему и присвоим имя aludec. На рисунке 10.17 приведена схема функциональная дешифратора инструкций. Следующим шагом произведем начертание УГО элемента как показано на рисунке 10.18

Добавить созданный элемент на главную схему. Выходы funct3 и funct7 блока дешифратора инструкций соединить с аналогичными входами блока дешифратора АЛУ.

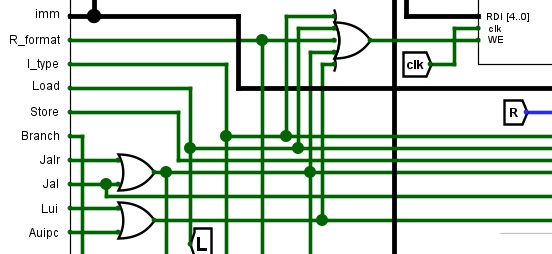

Выходы Jal и Jalr дешифратора инструкций объединить двухвходовым элементом "ИЛИ". Выход с данного элемента вывести на вход jump блока ALU dec. Вход alu_enable подключить к выходу двухвходового элемента "ИЛИ" входы которого подключить к выходам R_format и I_type дешифратора инструкций. На рисунке 10.19 показана схема включения ALU dec.

Вход мультиплексора управления записью в порт dataB АЛУ подключить к выходу 5-ти входового элемента "ИЛИ". Входы данного элемента следует подключить к выходным сигналам дешифратора инструкций: I_type, Load, Store, Jal. Выходы Lui и Auipc дешифратора инструкций объединить двухвходовым элементом "ИЛИ" и подключить к пятому входу "ИЛИ".

Выход Load дешифратора инструкций подключить к тоннелю с меткой L, также к тоннелю с данной меткой подключить вход OE оперативной памяти. Входы синхронизации блоков процессора подключить к тоннелю с меткой "CLK". Вход памяти WE подключить к линии, идущей к выходу Store дешифратора инструкций.

Добавить на схему двухвходовой 32-х разрядный мультиплексор. К входу 0 подключить выход rs1 регистрового файла. К входу 1 подключить выход Imem_addr счётчика инструкций PC. Вход управления данным мультиплексором подключить к выходу, предварительно добавленного двухвходового элемента "ИЛИ". Входы данного логического элемента подключить к выходам элемента "ИЛИ", объединяющего выходы Lui и Auipc дешифратора инструкций, и к выходу Jal данного блока.

Вход управления WE регистрового файла подключить к выходу предварительно добавленного пятивходового элемента "ИЛИ". Входы данного элемента необходимо подключить к выходам дешифратора: R_format, I_type, Load. Также два оставшихся входа подключить к выходам элементов "ИЛИ", объединяющих Lui и Auipc, а также Jal и Jalr. На рисунке 10.20 приведена схема организации управления входом WE регистрового файла.

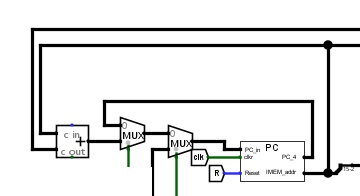

Блок счетчика инструкций дополнить сумматором и двумя мультиплексорами. Схема включения приведена на рисунке 10.21. Выход счетчика PC_4 соединить с входом 0 младшего мультиплексора. Выход данного мультиплексора соединить с входом 0 старшего мультиплексора. Выход старшего мультиплексора подключить к входу PC_in счетчика. Вход 1 младшего мультиплексора подключить к выходу сумматора. Один из входов сумматора подключить к выходу Imm дешифратора инструкций. Второй вход сумматора подключить к выходу счетчика Imem_addr.

Вход 1 старшего мультиплексора соединить с шиной, выходящей из мультиплексора оперативной памяти, но его необходимо соединить через разветвитель, где нулевой бит должен быть подключён к константе лог. "0". Остальные разряды берутся из шины (рисунок 10.22).

Вход управления старшего мультиплексора необходимо подключить к выходу элемента "ИЛИ", объединяющего выходы Jal и Jalrc дешифратора инструкций. Вход управления младшего мультиплексора следует подключить к предварительно добавленному двухвходовому элементу "И". Данный вход организуется с применением переходов Branch, рассмотренных ниже.

Для отладки режимов работы процессора к шинам данных регистрового файла, АЛУ, оперативной памяти следует подключить элементы "Датчик". Данный элемент находится в разделе "Проводка" и предназначен для наблюдения за сигналами при выполнении отладки схем.

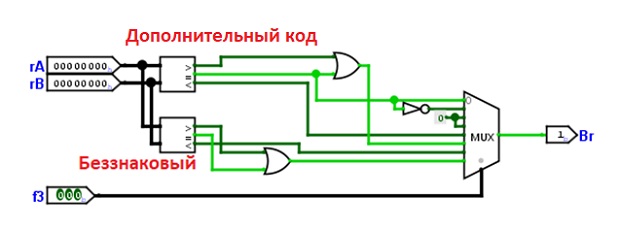

Для выполнения переходов необходимо создать дополнительный блок. Исходя из таблицы 10.1, данный блок активируется при наличии сигнала branch =63h и анализирует состояние поля funct3. Для реализации данного блока создадим новую схему. Наименование ей присвоим Branc_unit. В данную схему добавить два компаратора с разрядностью 32. Один со свойством "Формат числа" - "Дополнительный код". Второй со свойством "Формат числа" - "Беззнаковое". Далее на основании кодовой комбинации funct3, приведенной в таблице 10.2 произведём коммутацию выходов компараторов. Для этого добавим в схему мультиплексор со следующими параметрами:

- Выбирающие биты -3;

- Биты данных - 1;

- Разрешающий вход - нет.

Выход мультиплексора подключим к выходу с меткой "Br".

| Команда перехода | Вид перехода | Код funct3 |

|---|---|---|

| BEQ | при равенстве двух регистров | 000 |

| BNE | если два регистра не равны | 001 |

| BLT | если первый регистр меньше второго | 100 |

| BGE | если первый регистр больше второго | 101 |

| BLTU | если первый регистр меньше второго (беззнаковое сравнение) | 110 |

| BGEU | если первый регистр больше второго (беззнаковое сравнение) | 111 |

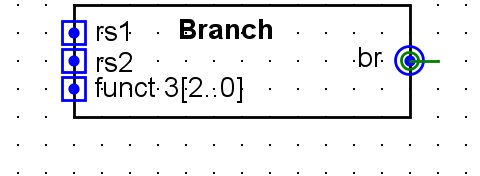

На рисунке 10.23 приведена схема функциональная блока условных переходов. На рисунке 10.24 ее графическое обозначение.

Созданный модуль должен быть объединен с выходом Branch блока управления. На рисунке 10.25 приведена схема управления процессора с использованием Branch_unit,