Проектирование счетчика инструкций, памяти инструкций и памяти данных

Практическая работа 9. Проектирование счетчика инструкций, памяти инструкций и памяти данных

Необходимые материалы для лекции Verilog-09.zip.

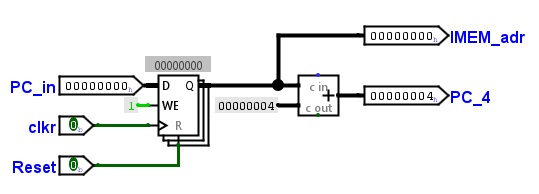

Исходя из описанных в разделе "Архитектора процессора" блоков процессора RISC-V, осуществим проектирование блока счетчика инструкций. Для этого в среде Logisim, в ранее созданном проекте cpu.circ, добавить новую схему. Присвоить ей имя PC. В созданной схеме добавить регистр с разрядностью 32. К входу данных регистра подключить 32-х разрядный вход. Свойству основание задать "шестнадцатеричное", а метке присвоить имя PC_in.

К выходу данных регистра подключить элемент выход. С такими же свойствами разрядности и основания как у PC_in. Имя присвоить IMEM_addr.

Добавить вход с именем "Reset", а также вход для синхронизации регистра. Имя метки синхронизации присвоить "clkr".

К входу WE регистра подключить однобитную константу лог. "1".

Так как выборка следующей инструкции осуществляется со смещением 4. Добавить на схему 32-х разрядный сумматор. Выход с регистра подключить к одному из входов сумматора. К второму входу сумматора подключить константу, также четырехразрядную = 4. К выходу результата сумматора подключить элемент выход. Имя метки присвоить PC_4.

Итоговая функциональная схема счетчика приведена на рисунке 9.1.

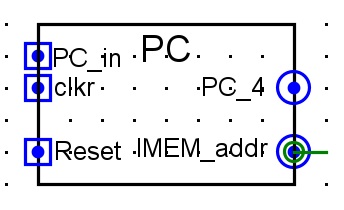

Далее получить УГО, проектируемого блока (рисунок 9.2).Необходимо обратить внимание на порядок размещения выходов при создании УГО счетчика инструкций.

В среде Logisim существуют два вида памяти (находятся в разделе "Память":

- постоянное запоминающее устройство (хранит данные постоянно) - ПЗУ (ROM);

- статическое оперативное запоминающее (изменяемые данные) - ОЗУ (RAM).

Для хранения инструкций - память инструкций IMEM будет применятся ПЗУ. Для хранения данных будет применятся ОЗУ.

В ПЗУ микропроцессора на кристалле загружается откомпилированная программа в машинных кодах посредством загрузочного кабеля если микропроцессор встроен либо посредством программатора.

В программируемой логике FPGA память может подготавливается также в виде скомпилированного файла и подгружаться в проект.

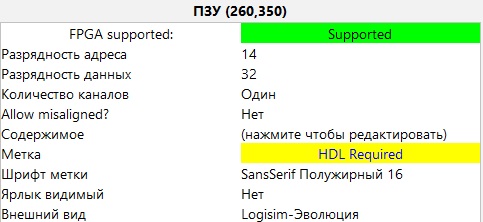

Для ПЗУ основные свойства:

- "Разрядность адреса" - определяет количество ячеек памяти;

- "Биты данных" - определяет разрядность данных ячеек памяти;

- "Содержимое" - указывает на путь к файлу, содержащему данные в машинных кодах.

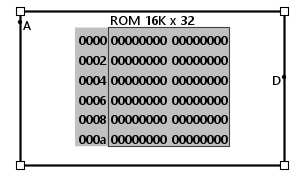

Разместим на поле main память ПЗУ с разрядностью адреса равной 14 и разрядностью данных равной 32, что соответствует емкости 16Кх32.

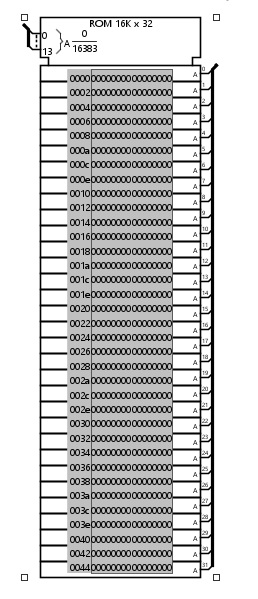

На рисунке 9.3а приведены настройки для ПЗУ, на рисунке 9.3b приведен сам блок. Слева у ПЗУ поле адреса, справа поле данных.

Для экономии пространства можно заменить свойство ПЗУ "Внешний вид" на Logisim-Классический (рисунок 9.4).

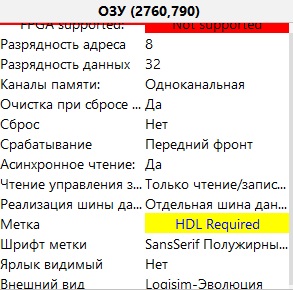

Для проекта процессора также необходима память данных для этого выберем ОЗУ Для ОЗУ основные свойства:

- "Разрядность адреса" - определяет количество ячеек памяти;

- "Биты данных" - определяет разрядность данных ячеек памяти;

- "Реализация шины данных" - определяет виды шин данных. Обычно шина данных на запись данных, отдельная шина данных на чтение.

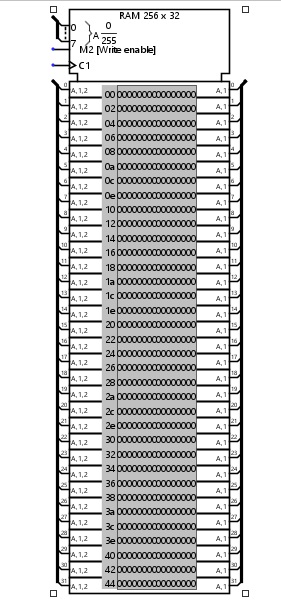

Разместим на поле main память ОЗУ с разрядностью адреса равной 8 и разрядностью данных равной 32, что соответствует емкости 256х32. Свойству "Каналы памяти" зададим "Одноканальная". Свойству "Реализация шины" данных зададим "Отдельная шина данных для чтения и записи". В свойстве "Асинхронное чтение" выберем "Да".

На рисунке 9.5a приведены настройки для ОЗУ, на рисунке 9.5b приведен сам блок. Слева у ПЗУ поле адреса, справа поле данных

Для уменьшения места, занимаемого памятью необходимо заменить свойство ОЗУ "Внешний вид" на Logisim-Классический (рисунок 9.6). На рисунке А - шина адреса, D (слева) - шина данных записи, справа - шина данных чтения. WE- write enable - вход управления разрешения записи в память, ОЕ - output enable вход управления разрешения чтения из памяти.