Регистровый файл RISC-V

Практическая работа 8. Регистровый файл RISC-V

Необходимые материалы для лекции Logisim-08.zip и Verilog-08.zip.

Базовая микроархитектура RISC-V представляет собой 32 разрядный процессор, содержащий 31 регистр общего назначения. Реализуем данный блок процессора.

Согласно структурной схеме процессора для проектируемого блока объявим следующие входы/выходы:

- rsi1(register source 1 address input) - вход адреса регистра первого аргумента;

- rsi2 (register source 2 address input) - вход адреса регистра второго аргумента;

- rdi (register destination address input) - вход адреса для записи в регистр;

- Data - вход данных для записи;

- clk_r - вход синхронизации;

- Reset - вход сброса;

- WE (write enable) - вход управления записи данных в регистр;

- rs1 (register source 1 data output) - выход данных регистра первого аргумента;

- rs2 (register source 2 data output) - выход данных регистра второго аргумента;

В созданном файле cpu.circ следует добавить новую схему, присвоить ей имя RegFile.

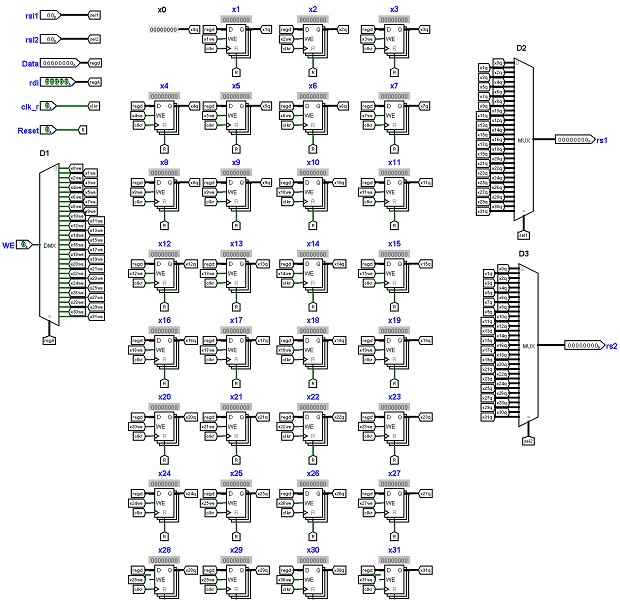

На поле разместить 31 регистр. Общее свойство всех регистров "Биты данных" задать равным 32. Регистры для удобства предлагается разместить в 4 столбцах. В каждом столбце 8 регистров. Единственное исключение регистр x0, так как данный регистр отбрасывает записываемые данные и всегда содержит 0. То соответственно в первом ряду вместо 4 регистров будет 3. Место регистра занимает константа лог. "0" разрядностью 32. Над константой разместить текст Х0. Остальным регистрам в свойстве "Метка" присвоить имена X1,X2,X3 и т.д.

Разместить на схеме демультиплексор (D1) со следующими свойствами:

- "выбирающие биты" - 5;

- "биты данных" - 1.

Вход данных демультиплексора подключить к входу, свойству "Метка" присвоить значение WE (write enable). В данном случае демультиплексор выполняет роль дешифратора адреса регистров при записи в них данных.

Разместить два мультиплексора D2, D3 со следующими свойствами:

- "выбирающие биты" - 5;

- "биты данных" - 32.

Мультиплексоры управляются раздельно, обеспечивая формирование двухканального выхода данных с регистров. Выход мультиплексора D2 подключить к 32-х разрядному выходу с меткой rs1, D3- rs2.

Связи внутри регистрового файла осуществляются посредством тоннелей. Их свойство "Биты данных" устанавливается в зависимости от подключения к соответствующим входам/выходам.

В таблице 8.1 приведены имена тоннелей с указанием подключения к элементам.

| Имя тоннеля | Вход | Выход |

|---|---|---|

| sel1 | Вход rsi1 (5 разрядов) | Адресный вход D2 |

| sel2 | Вход rsi2 (5 разрядов) | Адресный вход D3 |

| regd | Data (32 разрядf) | Входы D всех регистров |

| regA | Вход rdi (5 разрядов) | Адресный вход D1 |

| clkr | Вход clk_r (1 разряд) | Входы синхронизации всех регистров |

| R | Вход Reset (1 разряд) | Входы D всех регистров |

| x0we-x31we- | Выходы мультиплексора D1 | Соответствующие номеру Х входы WE регистров (X1-X31). Внимание: выход x0we никуда не подключается |

| x0q-x32q | Соответствующие номеру Х выходы Q регистров | Соответствующие номеру входу шины данных мультиплексоров D2 и D3 |

На рисунке 8.1 приведена схема функциональная проектируемого регистрового файла.

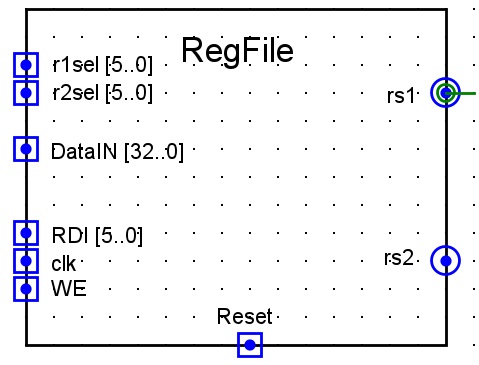

В инструменте "Редактировать внешний" вид создать УГО для данного элемента, подписав и разместив входы/выходы по функциональному признаку (рисунок 8.2)

Тестирование работоспособности созданного регистрового файла необходимо осуществить ввиду большого количества однообразных соединителей у регистров, а также однотипности схемы в целом. Если схема проектировалась методом копирования однотипных элементов, то риск неверной нумерации достаточно велик. Предлагаемый вариант тестирования схемы достаточно элементарный.

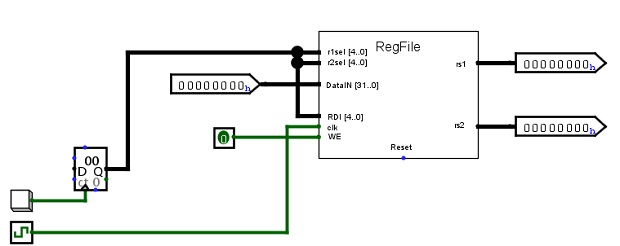

Для проверки корректности созданного регистрового файла в главной схеме проекта разместить непосредственно созданный блок (рисунок 8.3). К входу WE подключить элемент "контакт". К входам r1sel, r2sel, RDI подключить выход счетчика. Для счетчика задать свойство "Биты данных" - 5, свойство "Внешний вид" - "Logisim Классический". Остальные свойства не менять. Вход синхронизации счетчика подключить к элементу "кнопка" для ручного изменения адреса. Вход clk памяти подключить к тактовому генератору, частоту которого задать от 4Гц. Вход DataIn подключить к 32 разрядному входу. Установить на входе любое значение. К выходам rs1 и rs2 подключить 32 разрядные элементы "выход".

Установив на контакте управления WE, поочередно переключая кнопкой адреса регистров до 1f , убедиться, что данные на входе регистрового файла отображаются на выходах. После проверки созданные блоки и элементы следует удалить.

Для проектирования регистрового файла в среде Quartus, в существующем проекте RISC_V, создать новый Verilog HDL File. Сохранить файл как RegisterFile.v. Ввести код из листингa 8.1.

module RegisterFile(

input clk, // синхросигнал

input reset, // сигнал сброса

input regWrite, // сигнал разрешения записи в регистр

input [4:0] rs1, rs2, rd, // адреса регистров

input [31:0] writeData, // вход данных для записи

output [31:0] readData1, readData2 // выходные шины данных

);

reg [31:0] regs [0:31]; // регистровый файл

// Чтение регистров (асинхронное)

assign readData1 = regs[rs1];

assign readData2 = regs[rs2];

integer i;

// Синхронный сброс и запись в регистр

always @(posedge clk) begin

if (reset) begin

// Очистка всех регистров при активном сигнале сброса

for (i = 0; i < 32; i = i + 1) begin

regs[i] <= 32'd0;

end

end else if (regWrite && rd != 5'd0) begin

// Запись в регистр (кроме регистра x0, который всегда равен 0)

regs[rd] <= writeData;

end

end

endmodule

Листинг

8.1.

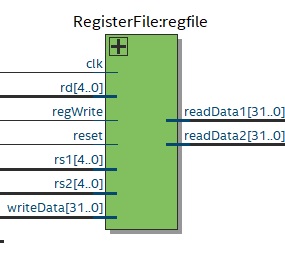

На рисунке 8.4 приведен вид RTL созданного модуля.