|

приветствую создателей курса и благодарю за доступ к информации! понимаю, что это уже никто не исправит, но, возможно, будут следующие версии и было бы неплохо дать расшифровку сокращений имен регистров итд, дабы закрепить понимание их роли в общем процессе. |

Лекция 3: Физическая и логическая организация адресного пространства

Сегментная организация памяти в защищенном режиме

В основе сегментной модели памяти лежит разделение ее на независимые адресные пространства переменной длины - сегменты. Для программы адресное пространство разделено на блоки смежных адресов, называемых сегментами, а программа может обращаться только к данным, находящимся в этих сегментах. Внутри сегментов применяется линейная адресация, то есть программа может обращаться к байту 0, байту 1 и т. д. Такая адресация осуществляется относительно начала сегмента, и физический адрес, ассоциируемый, например, с программным адресом 0, по существу, скрыт от программиста. Этот подход к управлению памятью опирается на тот факт, что программы обычно логически разделяются на области (сегменты) кода, данных и стека. При этом упрощается изоляция программ друг от друга в мультипрограммном режиме работы. Каждый сегмент имеет свое целевое назначение. Каждая задача имеет непосредственный доступ к трем основным сегментам: кода, данных и стека, определяемых сегментными регистрами CS, DS SS соответственно, и к трем дополнительным сегментам данных, определяемых сегментными регистрами ES, FS, GS. Описания этих сегментов содержатся в их дескрипторах. Любая программа, независимо от уровня ее привилегий, не может обращаться к сегменту до тех пор, пока он не описан с помощью дескриптора, а сам дескриптор не помещен в таблицу дескрипторов.

Дескрипторы хранятся либо в глобальной таблице дескрипторов (Global Descriptor Table - GDT), либо в локальных таблицах дескрипторов (Local Descriptor Table - LDT). В GDT содержатся дескрипторы сегментов, которые доступны всем активным задачам, имеющимся в системе на данный момент. GDT может содержать любые дескрипторы сегментов, за исключением дескрипторов прерываний и ловушек. Обычно GDT включает дескрипторы сегментов кодов и данных операционной системы, сегментов состояния задач и дескрипторы сегментов, содержащих локальные таблицы дескрипторов. Микропроцессорная система имеет единственную глобальную таблицу дескрипторов.

Локальная таблица дескрипторов LDT используется для хранения дескрипторов, доступных только данной задаче. Их количество определяется количеством активных задач в системе.

С точки зрения расположения в памяти, локальные таблицы дескрипторов представляют собой обычные сегменты. Они могут накладываться друг на друга, частично пересекаться. Это приводит к тому, что отдельные сегменты, описанные дескрипторами в своих LDT, могут разделяться несколькими задачами (рис. 3.8).

Для нахождения дескриптора в таблице дескрипторов используется селектор, который содержится в одном из сегментных регистров. Селектор представляет собой 16-разрядое слово, которое разбито на 3 поля (рис. 3.9):

- TI ( Table Indicator - индикатор таблицы ) показывает, к какой таблице идет обращение: TI = 0 - дескриптор находится в глобальной таблице дескрипторов GDT, TI = 1 - в локальной таблице LDT;

- Index: поле индекса - номер дескриптора в соответствующей таблице дескрипторов;

- RPL ( Request privilege level - уровень привилегий запроса ). При обращении сравнивается с полем DPL в байте доступа дескриптора.

Обращение разрешается, если уровень привилегий запроса не ниже, чем уровень привилегий дескриптора.

Максимальное количество дескрипторов, находящихся в таблице дескрипторов, определяется длиной поля Index селектора и равно 213. Так как каждый дескриптор имеет длину 8 байт, максимальный объем любой таблицы дескрипторов составляет 216 байт. Каждая из таблиц дескрипторов имеет регистр ( GDTR для глобальной таблицы и LDTR для локальной), определяющий ее положение в памяти. Регистр GDTR содержит 48 разрядов, из которых 32 задают базовый адрес глобальной таблицы дескрипторов, а 16 указывают ее объем в байтах (границу таблицы). Для определения положения дескриптора относительно начала таблицы его номер (поле Index селектора) умножается на 8, то есть реально сдвигается на три разряда влево, так как длина дескриптора составляет 8 байт. Если селектор обращается к дескриптору, содержащемуся в таблице GDT (при TI = 0 в селекторе), то полученное смещение сравнивается с хранящейся в GDTR границей таблицы. Если нарушения границы нет, то смещение прибавляется к содержащемуся в GDTR базовому адресу, в результате чего образуется физический адрес выбираемого дескриптора (рис. 3.10).

Нулевой дескриптор в GDT является пустым, не используемым. Селектор с нулевым значением разрядов 2….15 называется нуль-индикатором. Он обеспечивает обращение к нулевому дескриптору GDT. Так как этот дескриптор не используется, то при обращении к нему происходит прерывание. Одно из возможных применений пустых селекторов заключается в следующем. Перед инициированием задачи операционная система может загрузить в регистры DS и ES пустые селекторы. Если в последующем не инициализировать эти регистры, то адресация памяти через них вызовет особый случай (прерывание). Загрузка в LDTR пустого селектора, для которого поле Index = 0, допустима. Такая операция сообщает процессору о том, что в задаче не будет использоваться локальная дескрипторная таблица. Это характерно для небольших однопользовательских систем.

Для обращения к локальной таблице дескрипторов предназначен 16-разрядный регистр LDTR. Он содержит селектор, определяющий размещениев GDT дескриптора используемой локальной таблицы дескрипторов.

Такая структура упрощает работу с таблицами LDT. Благодаря описанию LDT с помощью селектора эти таблицы превращаются в обычные сегменты памяти и, в частности, могут размещаться в любых областях памяти, участвовать в свопинге и т. п. Внутри процессора с регистром LDTR ассоциируется так называемый "теневой регистр", в котором и хранится дескриптор LDT текущей задачи. Это ускоряет в последующем обращение к локальной таблице дескрипторов текущей задачи. При переключении с одной задачи на другую для замены используемой LDT достаточно загрузить в регистр LDTR селектор новой LDT, а процессор уже автоматически загрузит в теневой регистр дескриптор новой LDT при первом обращении к нему.

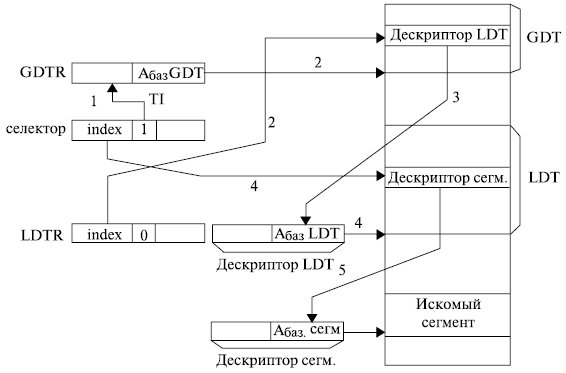

Если в селекторе индикатор таблицы TI = 1, то дескриптор сегмента выбирается из локальной таблицы дескрипторов. Процесс определения адреса сегмента в этом случае представлен на рис. 3.11.

Он более сложен по сравнению с получением дескриптора из глобальной таблицы дескрипторов и проходит следующие этапы:

- Анализируем, к какой из двух возможных таблиц дескрипторов идет обращение. Если в селекторе TI = 1, то обращение идет к локальной таблице дескрипторов.

- Находим дескриптор локальной таблицы дескрипторов в глобальной таблице дескрипторов.

- Считываем дескриптор LDT в "теневой" регистр регистра LDTR микропроцессора. После считывания дескриптора в "теневой" регистр дальнейшее обращение к сегменту аналогично обращению к GDT, где вместо GDT R используются поля базового адреса и предела из дескриптора LDTR, находящегося в "теневом" регистре.

- По адресу локальной таблицы дескрипторов, находящемуся в ее дескрипторе, и номеру дескриптора из обрабатываемого селектора находим дескриптор сегмента в локальной таблице дескрипторов.

- Записываем дескриптор сегмента в "теневой" регистр сегментного регистра микропроцессора для ускорения последующих обращений к искомому сегменту.

Таким образом, при обращении к сегменту через таблицу LDT появляется дополнительный уровень вложенности, снижающий быстродействие микропроцессора. "Теневые" регистры микропроцессора частично обеспечивают решение этой проблемы.

Поле адреса дескриптора, полученного из локальной или глобальной таблицы дескрипторов, определяет начало искомого сегмента. При суммировании полученного базового адреса сегмента и смещения в сегменте получается линейный адрес искомой ячейки памяти.

В случае если режим страничной адресации выключен (в регистре CR0 бит PG = 0), полученный линейный адрес равен физическому адресу искомого операнда или команды.

Рассмотрим подробнее процесс получения адреса операнда на примере команды

В этой команде нет специальных указаний об использовании сегмента, поэтому она обращается к текущему сегменту данных, селектор которого по умолчанию находится в сегментном регистре DS. Пусть (DS) = 0000000000011.0.XXb.

Формирование физического адреса операнда включает следующие действия (для сегментированного ЛАП):

- Образовать эффективный адрес (вычислить смещение в сегменте):

- Выбрать 3-й дескриптор ( Index = 3 ) из GDT (TI = 0).

Для этого:

- считать базовый адрес глобальной таблицы дескрипторов (

) из GDTR ;

) из GDTR ; - вычислить

;

; - обратиться по полученному адресу в память и считать нужный дескриптор.

- считать базовый адрес глобальной таблицы дескрипторов (

- Получить линейный адрес:

, где

, где  -базовый адрес сегмента из считанного дескриптора с номером 3.

-базовый адрес сегмента из считанного дескриптора с номером 3. - Так как при сегментной организации адресного пространства линейный адрес равен физическому, следует обратиться к памяти по сформированному адресу и передать двойное слово в EAX.

При TI = 1 потребовалось бы еще одно обращение к памяти для счтывания дескриптора LDT из GDT.

Чтобы сократить число обращений к памяти (а такой процесс должен проходить и при считывании кода каждой команды), в микропроцессорах с архитектурой IA-32 применяется так называемое кэширование дескрипторов. Кэширование опирается на тот факт, что обращение к памяти производятся гораздо чаще, чем изменение используемых сегментов и переключение задач. Поэтому с каждым регистром, содержащим селекторы тех или иных сегментов (сегментные регистры, а также регистры локальной таблицы дескрипторов LDTR и регистр задач TR ), ассоциируются "теневые", или кэш-регистры.

При первом считывании дескриптора, определяемого данным селектором, процессор автоматически считывает (кэширует) нужный дескриптор в соответствующий "теневой" регистр. Поскольку теперь дескриптор находится внутри МП, для получения линейного адреса памяти потребуется только сформировать эффективный адрес и просуммировать его с базовым адресом сегмента из нужного "теневого" регистра.

Так как программа обычно редко модифицирует регистры с селекторами, в защищенном режиме она будет выполняться примерно с такой же скоростью, как и в реальном режиме.

Помимо локальной и глобальной таблиц дескрипторов в микропроцессорной системе используется также дескрипторная таблица прерываний ( IDT ). Она содержит дескрипторы специальных системных объектов, которые определяют точки входа в процедуры обработки прерываний.

IDT служит заменой таблицы векторов прерываний 16-разрядного микропроцессора. Обращение к ней проводится только аппаратными средствами МП при возникновении аппаратных прерываний или особых случаев при выполнении программы. Программы самостоятельно не могут обратиться к IDT, так как единственный бит индикатора таблицы в селекторе сегмента идентифицирует только GDT или LDT.

До перевода процессора в защищенный режим необходимо создать таблицы GDT и IDT и соответственно инициализировать регистры GDTR и IDT R. Таблицы GDT и IDT определяются при загрузке в соответствующие регистры GDTR и IDT R базового адреса и предела. Это действие осуществляется только один раз в ходе подготовки к переходу в защищенный режим, и в дальнейшем содержимое GDTR и IDTR не изменяется. Это значит, что местонахождение таблиц GDT и IDT в известном смысле фиксировано, и они не могут участвовать в свопинге.