|

приветствую создателей курса и благодарю за доступ к информации! понимаю, что это уже никто не исправит, но, возможно, будут следующие версии и было бы неплохо дать расшифровку сокращений имен регистров итд, дабы закрепить понимание их роли в общем процессе. |

Лекция 3: Физическая и логическая организация адресного пространства

Структура кода команды и формирование смещения в сегменте

Как отмечалось выше, смещение в сегменте кода команд извлекается из регистра EIP и поэтому не требует дополнительных пояснений.

Механизм же формирования смещения в сегменте данных проводится на основе режима адресации операнда и требует отдельного изучения. Рассмотрим сначала структуру кода команды универсального 32-разрядного микропроцессора. Команды в архитектуре IA-32 имеют большое разнообразие форматов, которые зависят от типа операции, режимов адресации операндов, длины используемых непосредственных операндов и смещений и ряда других факторов. Они имеют длину от 1 до 15 байт. Все это существенно затрудняет их декодирование в МП с данной архитектурой. На рис. 3.5 представлен формат двухоперандной команды общего вида.

Команда может начинаться с нескольких необязательных байт (префиксов), которые определяют особенности выполнения команды. Префиксы размеров длины адреса и операндов позволяют изменить их значения, установленные по умолчанию битом размерности D в дескрипторе сегмента. Для операндов совместно с битом w, содержащимся в коде команды, префикс размера позволяет определить операнд длиной 8, 16 или 32 разряда. Префикс размера адреса определяет 16- или 32-разрядное смещение в сегменте (табл. 3.1).

| Бит размерности D в дескрипторе сегмента | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| Префикс размерности Операнда* | - | - | + | + | - | - | + | + |

| Префикс размерности адреса* | - | + | - | + | - | + | - | + |

| Разрядность операнда (бит) ** | 16/8 | 16/8 | 32/8 | 32/8 | 32/8 | 32/8 | 16/8 | 16/8 |

| Разрядность адреса (бит) | 16 | 32 | 16 | 32 | 32 | 16 | 32 | 16 |

Примечания:

** w = 1/0

В коде команды могут использоваться также дополнительные байты для префикса замены сегментного регистра, установленного по умолчанию, префикса повторения операции или префикса, предотвращающего прерывания операции перемещения данных.

Поле КОП содержит код выполняемой команды, а также бит w размерности используемых операндов. Для команд, применяющих непосредственный операнд, код операции может также занимать также часть постбайта.

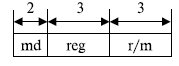

Постбайт (рис. 3.6) определяет местоположение операндов. Основная часть команд микропроцессора с архитектурой IA-32 позволяет работать только с одним операндом, находящимся в оперативной памяти. Его режим адресации кодируется полями md и r/m постбайта. Второй операнд либо извлекается из регистров общего назначения микропроцессора (его номер указывается в поле reg постбайта), либо кодируется в поле Imm самой команды (непосредственный операнд).

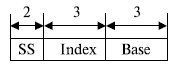

Байт масштабируемого индекса базы (SIB) служит для представления сложных структур памяти. На его наличие указывает код 100 в поле r/m постбайта. SIB-байт имеет следующую структуру (рис. 3.7):

Здесь SS - поле масштаба, Index задает номер одного из РОН, используемого в качестве индексного регистра (регистр ESP не может быть регистром индекса). Поле Base в комбинации с полем mod постбайта указывает регистр базы и смещение для индексированных операндов.

Применение SIB-байта позволяет формировать смещение в сегменте, иногда называемое эффективным адресом (ЭА), для операндов следующим образом:

![\mbox{(смещение в сегменте)} = [base] + [index]^{ss} + disp](/sites/default/files/tex_cache/25211e4e484fd72e0c187e825cbcfa80.png) |

( 3.1) |

где [base] - значение базового регистра, [index] - значение индексного регистра, ss - величина масштабного множителя, disp - значение смещения, закодированного в самой команде. В качестве базы или индекса может быть использован любой регистр общего назначения микропроцессора. Величина индекса может быть умножена на масштабный коэффициент (1, 2, 4 или 8), что дает возможность ссылки на элемент массива или записи соответствующей длины.

Смещение disp кодируется как величина со знаком в дополнительном коде. Его длина определяется значением бита D в дескрипторе сегмента, битом w в первом байте команды и наличием или отсутствием префикса разрядности адреса согласно табл. 3.1.

Этот механизм отражает основные усовершенствования в способах адресации операндов для 32-разрядной архитектуры IA-32 по сравнению с архитектурой x86. Различные комбинации слагаемых в выражении (3.1) дают следующие способы адресации памяти:

- прямая (только смещение),

- косвенная (только база),

- базовая относительная (база + смещение),

- индексная (индекс с масштабом),

- индексная со смещением (индекс с масштабом + смещение),

- базовая индексная (база + индекс с масштабом)

- относительная базовая индексная (база + индекс с масштабом + смещение).

Главные особенности формата команд МП с архитектурой IA-32 по сравнению с 16-разрядным микропроцессором:

- возможность использования любого из регистров общего назначения в любом из режимов адресации;

- возможность использования 32-разрядных непосредственных операндов и смещений при относительных режимах адресации наряду с имевшимися ранее 8- и 16-разрядными;

- добавление еще одного режима адресации - относительного базового индексного с масштабированием.