|

приветствую создателей курса и благодарю за доступ к информации! понимаю, что это уже никто не исправит, но, возможно, будут следующие версии и было бы неплохо дать расшифровку сокращений имен регистров итд, дабы закрепить понимание их роли в общем процессе. |

Архитектура однокристального микроконтроллера

Структура микроконтроллера МК-51

Архитектура однокристальных микроконтроллеров MCS-51, разработанная фирмой Intel, стала де-факто стандартной для этого типа микропроцессоров. Микропроцессоры, имеющие такую архитектуру, с определенными модификациями выпускаются различными фирмами. В нашей стране микроконтроллеры данной архитектуры относятся к семейству МК-51 и в настоящее время содержат следующие схемы: К1816ВЕ31, К1816ВЕ51, К1816ВЕ751, К1830ВЕ31, К1830ВЕ51. Все они являются функционально завершенными и содержат на кристалле все необходимые узлы для построения законченной системы управления минимальной конфигурации. Основные электрические характеристики этих схем представлены в табл. 14.1.

Все приведенные в табл. 14.1 м микроконтроллеры имеют емкость внутренней памяти данных в 128 бит и максимальную внешнюю тактовую частоту - 12 МГц.

Дальнейшее описание будет относиться к микросхеме К1816ВЕ51, если иное не оговорено особо.

Структурная схема МК-51 представлена на рис. 14.1.

МК содержит:

- арифметико-логический блок (АЛБ), включающий в себя:

- 8-разрядное АЛУ;

- внутреннюю память программ емкостью 4 Кбайт, в которой также могут храниться константы;

- внутреннюю память данных емкостью 128 байт, используемую для организации банков регистров общего назначения, стека и хранения пользовательских данных; часть этой памяти имеет побитовый доступ;

- 32 двунаправленных интерфейсных линии, индивидуально настраиваемых на ввод или вывод информации и организованных в виде четырех 8-разрядных портов P0-P3;

- два 16-разрядных многорежимных таймера/счетчика TC0 и TC1, используемых для организации временных задержек, внешних событий (количества сигналов, поступающих по внешним входам Т0 и Т1) и тактирования последовательного порта;

- двунаправленный дуплексный асинхронный последовательный порт;

- двухуровневую приоритетную маскируемую систему прерываний от трех внутренних источников (таймеров/счетчиков и последовательного порта) и двух внешних, поступающих по входам INT0 и INT1;

- устройство управления (УУ);

- встроенный тактовый генератор (ТГ), тактирование которого проводится внешним генератором с частотой fBQ; частота машинного цикла составляет fBQ / 12, время выполнения команд МК составляет 1-4 периода машинного цикла.

Формат регистра PSW представлен в табл. 14.2.

Организация памяти

Одной из основных особенностей однокристальных микроконтроллеров, отличающих их от других типов микропроцессорных БИС, является так называемая "гарвардская архитектура", при которой память программ и память данных физически и логически отделены друг от друга.

Память данных

Память данных, расположенная на кристалле (внутренняя память данных), имеет емкость 128 байт с адресами 00h-7Fh. Она может быть расширена до 64 Кбайт за счет подключения блоков внешней памяти данных.

Помимо возможности использования ОЗУ в качестве массива оперативной памяти, отдельные ее области имеют самостоятельное значение. Часть ОЗУ применяется в качестве регистров общего назначения, часть имеет прямоадресуемый доступ к отдельным битам, образуя так называемую битовую память. В ОЗУ располагается также и область стека.

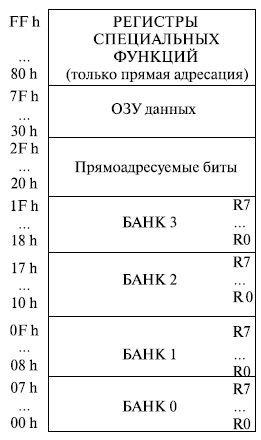

Распределение адресного пространства ОЗУ показано на рис. 14.2.

Младшие 32 байта внутреннего ОЗУ данных сгруппированы в 4 банка по 8 регистров общего назначения в каждом (БАНК 0-БАНК 3). Определение рабочего в данный момент банка, то есть банка регистров, к которому обращается программа при использовании имен R0-R7, осуще ствляется установкой битов RS0 и RS1 в регистре слова состояния PSW.

Наличие нескольких банков регистров сокращает длину команд за счет уменьшения длины поля номера регистра, а также уменьшает время, необходимое для сохранения и восстановления регистров при работе с подпрограммами и обработчиками прерываний, что характерно для структуры задач, решаемых микроконтроллерами.

ОЗУ данных с адресами 20h-2Fh образует область ячеек, к которым возможен побитный доступ. Система команд МК-51 содержит значительное количество инструкций, позволяющих работать с отдельными битами, используя при этом прямую адресацию. 128 бит, составляющие рассматриваемую область внутреннего ОЗУ данных, имеют адреса бит 00h-7Fh и предназначены для работы с такими инструкциями. Таким образом, к ячейке с адресом, например, 21h можно обратиться как к байту, используя ее прямой адрес 21h, а можно обратиться к ее отдельным битам с помощью команд, работающих с битовой информацией. При этом младший бит этого байта имеет адрес 08h, а старший - 0Fh.

Ячейки памяти с адресами 30h-7Fh используются как обычная оперативная память.

Во внутреннем ОЗУ данных размещается также область стека. Ее положение не фиксировано, а определяется значением указателя стека SP.

Адресное пространство внутренней памяти данных с адресами 80h-FFh отведено под указание регистров специальных функций микропроцессора. Область регистров специальных функций содержит регистры-защелки портов ввода-вывода, регистры таймеров/счетчиков, регистры управления и т. п. Эти регистры допускают только прямую адресацию.

Все ячейки внутреннего ОЗУ данных могут адресоваться с использованием прямой и косвенной адресации. Обращение к регистрам специальных функций допускается с применением только прямой адресации.

К внешней памяти данных можно обращаться только на запись или чтение с помощью специальных команд. Эти команды осуществляют обмен информацией между внешней памятью данных и аккумулятором микроконтроллера и не влияют на внутреннюю память данных МК. Таким образом, в системе могут одновременно присутствовать внутренняя память данных с адресами 00h-0Fh и внешняя память данных с адресами 0000h-FFFFh.