|

приветствую создателей курса и благодарю за доступ к информации! понимаю, что это уже никто не исправит, но, возможно, будут следующие версии и было бы неплохо дать расшифровку сокращений имен регистров итд, дабы закрепить понимание их роли в общем процессе. |

Микропроцессор и его архитектура

Остановимся вкратце на их рассмотрении.

К основным нововведениям микропроцессора i486, выпущенного в 1989 году, относятся два, которые связаны с расширившимися технологическими возможностями. Это размещение непосредственно на кристалле БИС двух важных блоков, которые раньше выполнялись в виде отдельных микросхем: кэш-памяти и блока процессора обработки чисел с плавающей точкой ( floating point unit - FPU ). Кэш-память имела объем 8

Кбайт и предназначалась для хранения программ и данных. FPU имел внутренний файл из восьми 80-разрядных регистров, свой регистр состояния и управления.

Главной отличительной чертой нового продукта в линейке 32-разрядных микропроцессоров - МП Pentium - явилась возможность конвейерной обработки информации. Хотя некоторые авторы считают, что конвейер появился уже в i486, это не является общепринятым мнением.

Высокая скорость выполнения команд в МП Pentium достигалась благодаря двум 5-ступенчатым конвейерам, позволявшим одновременно исполнять несколько инструкций. Обмен информацией с памятью через кэш данных осуществлялся независимо от процессорного ядра, а буфер инструкций был связан с ним через высокоскоростную 256-разрядную внутреннюю шину. Несмотря на то что новый кристалл был спроектирован как 32-разрядный, для связи с остальными компонентами системы использовалась внешняя 64-разрядная шина данных. Появление конвейера обусловило необходимость введения еще одного блока - схемы предсказания переходов. Эффективная работа данной схемы чрезвычайно важна для повышения производительности микропроцессора. Все последующие модификации микропроцессоров непременно связаны с улучшением ее работы.

Основным нововведением разработанного в 1997 году микропроцессора Pentium MMX стал блок, обеспечивавший новую схему обработки целочисленной информации - SIMD (Single Instruction - Multiple Data: одна команда - множество данных). До этого обработка велась по классической схеме SISD: каждая команда выполняла действия над своей парой операндов. Введение SIMD-операций позволило обрабатывать одновременно несколько операндов с использованием одной команды, что дало возможность существенно поднять производительность микропроцессора на тех задачах, где над большими массивами однородной информации выполнялись одинаковые операции, например, в мультимедийных приложениях. Появление таких возможностей потребовало введения в систему команд 57 новых инструкций, но регистровая структура микропроцессора не изменилась.

Микропроцессор Pentium III, появившийся в 1999 году, позволил обрабатывать по схеме SIMD не только целочисленные операнды, но и числа с плавающей точкой. Для этого система команд была расширена на 70 инструкций, а в структуре микропроцессора появился специальный блок SSE, содержащий, в частности, отдельный регистровый файл из восьми 128-разрядных регистров. Еще одной новинкой, использованной в Pentium III, было размещение на кристалле кэш-памяти второго уровня (начиная с ядра Coppermine), работающей на частоте ядра. Но это носило скорее количественный характер и не внесло существенных изменений в архитектуру.

Микропроцессор Pentium 4 завершает линейку 32-разрядных микропроцессоров. Основным вкладом этого микропроцессора в развитие архитектуры IA-32 стало еще большее увеличение глубины конвейера - до 31 стадии, что позволило сильно нарастить частоту процессора. Количество конвейеров возросло до 9. Кроме поддержки ставших традиционными инструкций MMX и SSE, в Pentium 4 добавили еще 144 команды SSE2, затем и SSE3, ориентированные в первую очередь на работу с потоковыми данными.

В 2001 году фирмой Intel был выпущен микропроцессор Itanium, положивший начало новой 64-разрядной архитектуре - IA-64, которая сменила архитектуру 32-разрядных микропроцессоров IA-32, господствовавшую на протяжении более 15 лет.

Данное учебное пособие в части универсальных микропроцессоров будет базироваться в основном на рассмотрении базовой архитектуры 32- разрядного микропроцессора, которая сложилась в микропроцессоре i486. Основные моменты, касающиеся развития этой архитектуры (конвейерная организация работы, обработка информации по схеме SIMD и т. д.), будут рассмотрены отдельно. Также отдельно будут рассмотрены современные направления развития архитектуры универсальных микропроцессоров и, в качестве примера, архитектура 80-ядерного микропроцессора фирмы Intel и микропроцессора Itanium.

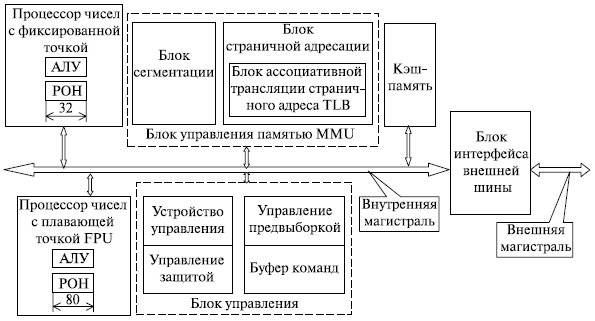

Структура 32-разрядного универсального микропроцессора

Рассмотрение архитектуры IA-32 начнем с микропроцессора i486. В нем впервые появились те блоки, которых не было на кристалле первого 32-разрядного микропроцессора i386, - кэш-память и процессор обработки чисел с плавающей точкой. Именно его архитектуру можно рассматривать как базовую для IA-32. Структура микропроцессора i486 представлена на рис. 1.3.

Рассмотрим состав и назначение основных блоков этого микропроцессора.

Процессор обработки чисел с фиксированной точкой содержит 32-разрядное АЛУ и блок регистров общего назначения. АЛУ предназначено для обработки двоичных чисел длиной 1, 2 или 4 байта без знака или со знаком, а также двоично-десятичных чисел, не превышающих 99. Двоичные числа со знаком представляются в дополнительном коде. Блок регистров общего назначения содержит восемь 32-разрядных регистров, часть из которых допускает 16- и 8-разрядное обращение.

Процессор обработки чисел с плавающей точкой состоит из 80-разрядного АЛУ, блока из восьми 80-разрядных регистров общего назначения, а также управляющих регистров. Главным образом он предназначен для обработки чисел с плавающей точкой, но также используется для обработки целых чисел со знаком длиной 8 байт и двоично-десятичных чисел величиной от 100 до 99…9 (18 цифр). На первых этапах развития SIMD-обработки регистры FPU использовались для хранения операндов, представленных в новых форматах.

Блок управления памятью (Memory Management Unit - MMU) состоит из двух основных блоков в соответствии с организацией памяти.

В общем случае память в микропроцессоре делится на сегменты, которые, в свою очередь, делятся на страницы. В соответствии с этим, MMU содержит блок сегментации (или блок сегментного преобразования адреса) и блок страничного преобразования, в состав которого входит так называемый буфер ассоциативной трансляции адресов стра- ниц (TLB).

Кэш-память представляет собой промежуточную ступень между оперативной памятью и регистрами микропроцессора и предназначена для хранения наиболее часто используемой информации.

В состав блока управления входят:

- собственно устройство управления, то есть та классическая схема, которая под действием кода команды вырабатывает набор управляющих сигналов, поступающих на разные узлы как самого микропроцессора, так и на блок интерфейса внешней шины;

- управление защитой памяти: обеспечивает аппаратную защиту программ и данных при управлении памятью и по привилегиям;

- блок управления предвыборкой команд: реализует опережающее заполнение буфера команд, представляющего собой некоторую буферную память. Буфер команд имеет емкость 32 байта и заполняется командами из следующих ячеек памяти команд по мере своего освобождения. Этим обеспечивается ускорение обработки микропроцессором следующей команды. Данный блок подвергался, пожалуй, наиболее существенным переработкам по мере развития архитектуры IA-32 - причина в широком последующем использовании конвейерной организации работы МП и связанной с этим необходимости постоянного совершенствования блока предсказания адреса следующей команды.

Блок интерфейса внешней шины осуществляет электрическое согласование параметров внутренней магистрали с сигналами внешних магистралей, формирование необходимых сигналов на внешнюю магистраль и прием сигналов извне. Внешняя магистраль микропроцессора состоит из шины адреса, шины данных и сигналов управления:

- шина данных имеет ширину 32 разряда;

- 32-разрядный адрес передается по 34-разрядной шине А31...А2+(B3,B2,B1,B0). Чтобы с минимальными потерями согласовывать 32-разрядную шину данных с передачей данных меньшей разрядности, младшие разряды адреса (А1 и А0) передаются в дешифрированном виде (B3, B2, B1, B0). Они показывают, какие байты из 32-разрядной шины данных в данный момент реально востребованы: 1 байт, 2 младших байта, 2 старших байта либо все 32 разряда данных;

- шина управления - 32-разрядная. По ней передаются сигналы записи и чтения содержимого оперативной памяти и внешних устройств, сигналы запросов прерываний, прямого доступа к памяти и т. д.

Особый интерес представляют три режима работы микропроцессора: реальный, защищенный и режим виртуального МП i8086. В реальном режиме обеспечивается совместимость на уровне объектных кодов с микропроцессором i8086 и микропроцессором i286, работающем в реальном режиме. В этом режиме архитектура 32-разрядного микропроцессора почти полностью идентична архитектуре 16-разрядного МП. Для программиста же он вообще представляется как МП i8086, выполняющий написанные программы с большей скоростью и обладающий расширенной системой команд и регистрами. Благодаря этим качествам фирма Intel сохранила прежних клиентов, которые хотели модернизировать свои системы, не отказываясь от имевшегося задела в области программного обеспечения, и привлекла тех, кому изначально требовалась высокая скорость обработки информации.

Одно из основных ограничений реального режима было связано с предельной емкостью адресуемой памяти, равной 1 Мбайт. От него свободен защищенный режим, позволяющий воспользоваться всеми преимуществами архитектуры нового МП. Размер адресного пространства в этом случае увеличивается до 4 Гбайт, а общий объем поддерживаемого адресного пространства - до 64 терабайт (1 Тбайт = 240 байт). МП, работающие в защищенном режиме, обладают более высоким быстродействием и возможностями организации истинной многозадачности.

Наконец, режим виртуального МП открывает возможность одновременного исполнения программ, написанных для МП i8086, i286 и i386.

Поскольку емкость памяти, адресуемой микропроцессором, не ограничена значением 1 Мбайт, этот режим позволяет формировать несколько виртуальных сред i8086.

Краткие итоги. В лекции даны определения микропроцессора и микропроцессорной системы, архитектуры микропроцессора. Приведена классификация микропроцессоров по их архитектуре, представлены параметры, которые характеризуют микропроцессоры каждого класса как вычислительное устройство и как электронное изделие. Рассмотрены этапы развития архитектуры универсальных микропроцессоров на примере МП БИС фирмы Intel, занимающей доминирующее положение в этом секторе рынка. Описаны структура и основные блоки микропроцессора i486, являющегося базовым микропроцессором для этой архитектуры.