|

Добрый день!

Скажите, пожалуйста,планируется ли продолжение курсов по нанотехнологиям? Спасибо, Евгений

|

Термальный синтез микропрограмм алгоритмически ориентированных МКМД-бит-потоковых субпроцессоров

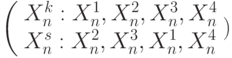

В этом случае аппаратно-временные затраты на ассоциативные слов-инструкции  не возрастают, так как дешифрации подлежит только значащая часть адресов

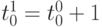

не возрастают, так как дешифрации подлежит только значащая часть адресов  , в чем можно убедиться, сравнив PD - и DD -ассоциативные конструкции рисунков 5.9 и 5.10, где

, в чем можно убедиться, сравнив PD - и DD -ассоциативные конструкции рисунков 5.9 и 5.10, где  , а

, а  равняется соответственно 6 и 8 битам.

равняется соответственно 6 и 8 битам.

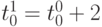

В обоих случаях параметры схемы соответствуют подстановке:

|

( 5.13) |

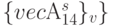

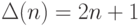

но в DD -ассоциативной конструкции рис. 5.10 поток формальных адресов  необходимо предварительно модифицировать в поток загружаемых адресов

необходимо предварительно модифицировать в поток загружаемых адресов  по правилу:

по правилу:

|

( 5.14) |

где ![\lambda = mod_{8}[(s-1)(8-mod_{8}n_{X} )]](/sites/default/files/tex_cache/b3524157b9299028aaf62a5bb9df007c.png) определяет фазовый сдвиг

определяет фазовый сдвиг  , связанный с некратным

, связанный с некратным  циклическим воспроизводством

циклическим воспроизводством  в бит-инструкциях

в бит-инструкциях  , где

, где  бит.

бит.

Согласно (5.14) для подстановки (5.13) получим:

-

, то

, то  ;

; -

, то

, то  ;

; -

, то

, то  ;

; -

, то

, то  .

.

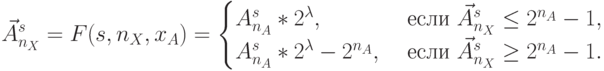

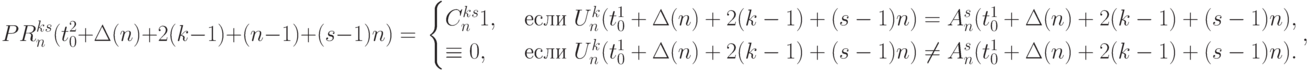

Рассмотренные PD - и DD -ассоциативные конструкции слов-инструкций  работают по правилам:

работают по правилам:

- для рис. 5.9:

( 5.15) где

такта, а

такта, а  тактов - технологическая задержка в слов- инструкции

тактов - технологическая задержка в слов- инструкции  ;

; - для рис. 5.10:

( 5.16) где

такт,

такт,  такта, а

такта, а  в данном случае составляет 6 тактов.

в данном случае составляет 6 тактов.

При  PD -ассоциативные конструкции применимы не только в супрамолекулярной, но и в современной опто- или микроэлектронике, так как в этом случае системные временные издержки на синтез специфических

PD -ассоциативные конструкции применимы не только в супрамолекулярной, но и в современной опто- или микроэлектронике, так как в этом случае системные временные издержки на синтез специфических  для каждой подстановки

для каждой подстановки  можно окупить за счет {\alpha}-циклов их использования. Для этого достаточно в поток-инструкциях

можно окупить за счет {\alpha}-циклов их использования. Для этого достаточно в поток-инструкциях

-кратно использовать одни и те же PD -ассоциативные слов-инструкции

-кратно использовать одни и те же PD -ассоциативные слов-инструкции  рис. 5.11, которые выполнены по схеме целочислен-ного сравнения

рис. 5.11, которые выполнены по схеме целочислен-ного сравнения  .

.

В результате в поток-инструкциях  со встроенными блоками

со встроенными блоками  :

:

- сохраняется структурно-функциональная схема

, но топологические схемы всех составляющих ее слов-инструкций полностью изменяются, так как одна

, но топологические схемы всех составляющих ее слов-инструкций полностью изменяются, так как одна  обычно занимает две и более строк бит-процессоров;

обычно занимает две и более строк бит-процессоров; - этап синтеза слов-инструкций

для каждой

для каждой  -й перестановки совмещается во времени с этапом

-й перестановки совмещается во времени с этапом  -кратного использования

-кратного использования  при исполнении

при исполнении  -й подстановки длительностью

-й подстановки длительностью  тактов или

тактов или  тактов в зависимости от типа используемого порта вывода.

тактов в зависимости от типа используемого порта вывода.

Поток-инструкции TRANS со встроенными блоками PD-ассоциативной памяти

В разделе 8.4 курса "Задачи и модели вычислительных наноструктур" на примере умножителей показано, что функция "хранение" (  ) является атрибутивной для PD -ассоциативных слов-инструкций. Поэтому любую из них можно использовать в поток-инструкциях

) является атрибутивной для PD -ассоциативных слов-инструкций. Поэтому любую из них можно использовать в поток-инструкциях  вместо циклических FIFO -регистров

вместо циклических FIFO -регистров  с тем ограничением, что такие слов-инструкции обеспечивают "хранение" переставляемых потоков данных

с тем ограничением, что такие слов-инструкции обеспечивают "хранение" переставляемых потоков данных  только на одном цикле

только на одном цикле  . В этом случае в супрамолекулярных вычислителях синтез структурно адаптируемых под содержимое потока

. В этом случае в супрамолекулярных вычислителях синтез структурно адаптируемых под содержимое потока  ячеек памяти

ячеек памяти  можно совместить во времени с фазой "чтения"

можно совместить во времени с фазой "чтения"  другой,

другой,  -й PD -ассоциативной конструкции

-й PD -ассоциативной конструкции  ..

..

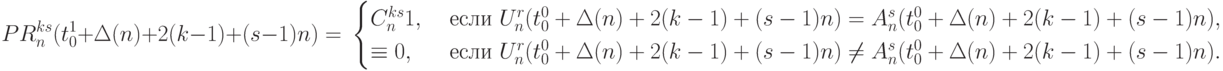

Сам синтез PD -ассоциативных  можно проводить:

можно проводить:

- в порядке "чтения" (рис. 5.12-а, когда синтезируемые слов-инструкции (в данном случае это

размещаются в пространстве в порядке подстановки, то есть по индексу

размещаются в пространстве в порядке подстановки, то есть по индексу  ;

;

увеличить изображение

Рис. 5.12. Топологические схемы микропрограмм PD-ассоциативного хранения (MEMORY_PD) - в порядке "записи" (рис. 5.12-б, когда синтезируемые слов-инструкции (в данном случае это смесь

размещаются в пространстве в порядке поступления, то есть по индексу

размещаются в пространстве в порядке поступления, то есть по индексу  .

.