|

Добрый день!

Скажите, пожалуйста,планируется ли продолжение курсов по нанотехнологиям? Спасибо, Евгений

|

Термальный синтез микропрограмм алгоритмически ориентированных МКМД-бит-потоковых субпроцессоров

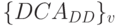

Как и всякая ассоциативная конструкция,  требует доопределения задающих ее формальных соотношений (5.1)-(5.5) содержимым пространственно-временных потоков данных, которые используются в качестве управляющих. В данном случае к ним относятся

требует доопределения задающих ее формальных соотношений (5.1)-(5.5) содержимым пространственно-временных потоков данных, которые используются в качестве управляющих. В данном случае к ним относятся  ,

,  и

и  , которые задают соответственно цикл выполнения перестановки

, которые задают соответственно цикл выполнения перестановки  и разрядность

и разрядность  переставляемых операндов. Более того, условия правильной работы слов-инструкций

переставляемых операндов. Более того, условия правильной работы слов-инструкций  доопределяются содержимым потоками преобразуемых данных

доопределяются содержимым потоками преобразуемых данных  и

и  обеспечивающих синфазную и синхронную работу всех слов-инструкций, входящих в

обеспечивающих синфазную и синхронную работу всех слов-инструкций, входящих в  .

.

Тем не менее, для однозначного задания условий правильной работы ассоциативной поток-инструкции  , а с ними и выполняемого ею преобразования

, а с ними и выполняемого ею преобразования  , этого недостаточно. Объясняется это тем, что в "сложных" ассоциативных конструкциях содержимое информационных и управляющих потоков задает только необходимые условия их правильной работы. Полное устранение неоднозначности в таких конструкциях требует выполнения фазовых соотношений между всеми потоками управляющих и преобразуемых данных в процессе их распространения по составляющим слов-инструкциям, как по горизонтали, то есть в каждой

, этого недостаточно. Объясняется это тем, что в "сложных" ассоциативных конструкциях содержимое информационных и управляющих потоков задает только необходимые условия их правильной работы. Полное устранение неоднозначности в таких конструкциях требует выполнения фазовых соотношений между всеми потоками управляющих и преобразуемых данных в процессе их распространения по составляющим слов-инструкциям, как по горизонтали, то есть в каждой  -й линейной последовательности

-й линейной последовательности  , так и по вертикали, то есть по всей совокупности таких последовательностей. При этом параметр

, так и по вертикали, то есть по всей совокупности таких последовательностей. При этом параметр  входит в (5.1)-(5.5) только контекстно, так как он задает период активности поток-инструкции и поэтому используется в устройстве управления

входит в (5.1)-(5.5) только контекстно, так как он задает период активности поток-инструкции и поэтому используется в устройстве управления  -шиной субпроцессора, а не в устройстве управления потоками данных.

-шиной субпроцессора, а не в устройстве управления потоками данных.

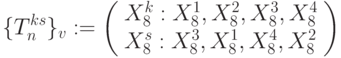

Сказанное иллюстрирует табл. 5.1 для подстановки вида:

|

( 5.6) |

а) выходы дешифратора (  ) )

| |||||||

|---|---|---|---|---|---|---|---|

| Значение | 0 | 1 | 0 | 0 | |||

| Такт | 18 | 26 | 34 | 42 | |||

| Значение | 0 | 0 | 0 | 1 | |||

| Такт | 17 | 25 | 33 | 41 | |||

| Значение | 1 | 0 | 0 | 0 | |||

| Такт | 16 | 24 | 32 | 40 | |||

| Значение | 0 | 0 | 1 | 0 | |||

| Такт | 15 | 23 | 31 | 39 | |||

б) входы кольцевых FIFO-регистров (  ) )

| |||||||

| 0 |  |

|

|

||||

| Такт | 20 | 28 | 36 | 44 | |||

| Значение | 0 | 0 | 0 |  |

|||

| Такт | 19 | 27 | 35 | 43 | |||

| Значение |  |

|

|

|

|||

| Такт | 18 | 26 | 34 | 42 | |||

| Значение | 0 | 0 |  |

|

|||

| Такт | 17 | 25 | 33 | 41 | |||

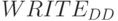

| в) выходы схем "И" кольцевых FIFO-регистров (MEMORY_{DD}) | |||||||

| Значение | 0 |  |

|

|

|

|

0 |

| Такт | 25 | 33 | 41 | 49 | 57 | 65 | 73 |

| Значение | 0 | 0 | 0 |  |

|

|

0 |

| Такт | 24 | 32 | 40 | 48 | 56 | 64 | 72 |

| Значение |  |

|

|

|

|

|

0 |

| Такт | 23 | 31 | 39 | 47 | 55 | 63 | 71 |

| Значение | 0 | 0 |  |

|

|

|

0 |

| Такт | 22 | 30 | 38 | 46 | 54 | 62 | 70 |

г) входы схемы "ИЛИ" порта вывода (  ) )

| |||||||

| Значение | 0 | 0 | 0 | 0 | 0 | 0 |  |

| Такт | 25 | 33 | 41 | 49 | 57 | 65 | 73 |

| Значение | 0 | 0 | 0 | 0 | 0 |  |

0 |

| Такт | 24 | 32 | 40 | 48 | 56 | 64 | 72 |

| Значение | 0 | 0 | 0 | 0 |  |

0 | 0 |

| Такт | 23 | 31 | 39 | 47 | 55 | 63 | 71 |

| Значение | 0 | 0 | 0 |  |

0 | 0 | 0 |

| Такт | 22 | 30 | 38 | 46 | 54 | 62 | 70 |

д) выходы схемы "ИЛИ" порта вывода (  ) )

| |||||||

| Значение |  |

|

|

|

|||

| Такт | 50 | 58 | 66 | 74 | |||

| Значение |  |

|

|

0 | |||

| Такт | 49 | 57 | 65 | 73 | |||

| Значение |  |

|

0 | 0 | |||

| Такт | 48 | 56 | 64 | 72 | |||

| Значение |  |

0 | 0 | 0 | |||

| Такт | 47 | 55 | 63 | 71 | |||

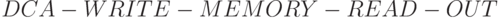

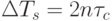

Из (5.1)-(5.5) видно, что в FIFO -регистровой памяти фаза записи выполняется параллельно, а фаза чтения - последовательно. Однако, как и в ЗУПВ, из-за разделения этих фаз во времени пропускная способность по потоку входных данных и здесь снижается в 2 раза, что увеличивает и период дискретизации по Котельникову:  , где

, где  - длительность такта работы бит-матрицы. Коэффициент векторизации каждой

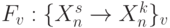

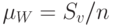

- длительность такта работы бит-матрицы. Коэффициент векторизации каждой  -й фазы записи

-й фазы записи  определяется условием распространения

определяется условием распространения  и

и  по соответствующим каналам транзита. Заменив эти каналы на каналы транзита с задержкой, можно увеличить в 2 раза количество одновременно дешифруемых

по соответствующим каналам транзита. Заменив эти каналы на каналы транзита с задержкой, можно увеличить в 2 раза количество одновременно дешифруемых  , а с ними и коэффициент распараллеливания фазы записи

, а с ними и коэффициент распараллеливания фазы записи  в

в  . Однако в этом случае повышается в 2 раза только пользовательская производительность (то есть пропускная способность по потоку команд), но не пропускная способность

. Однако в этом случае повышается в 2 раза только пользовательская производительность (то есть пропускная способность по потоку команд), но не пропускная способность  по потоку данных.

Это связано с тем, что поток данных

по потоку данных.

Это связано с тем, что поток данных  распространяется последовательно по слов-инструкциям

распространяется последовательно по слов-инструкциям  , а его значащая часть по определению не может занимать меньше

, а его значащая часть по определению не может занимать меньше  тактов из

тактов из  тактов всего

тактов всего  -го цикла "записи-чтения". Поэтому повысить пропускную способность

-го цикла "записи-чтения". Поэтому повысить пропускную способность  по потоку данных до предельно возможной с

по потоку данных до предельно возможной с  можно только за счет совмещения во времени фаз записи и чтения. Но в DD -ассоциативных MIMD-бит-потоковых конструкциях для этого нет необходимости прибегать к избыточной (по аппаратным затратам на

можно только за счет совмещения во времени фаз записи и чтения. Но в DD -ассоциативных MIMD-бит-потоковых конструкциях для этого нет необходимости прибегать к избыточной (по аппаратным затратам на  ) парафазной схеме, как это имеет место в вычислителях на основе ЗУПВ.

В данном случае достаточно в порт вывода ввести

) парафазной схеме, как это имеет место в вычислителях на основе ЗУПВ.

В данном случае достаточно в порт вывода ввести  буфер-ных FIFO -регистров общей емкостью

буфер-ных FIFO -регистров общей емкостью  бит (рис. 5.6). В этом случае в фазе

бит (рис. 5.6). В этом случае в фазе  выполняется "параллельно" и все

выполняется "параллельно" и все  считываются из кольцевых FIFO -регистров с задержкой на 1 такт. В результате, как и в парафазной схеме ЗУПВ, удается совместить во времени фазу записи

считываются из кольцевых FIFO -регистров с задержкой на 1 такт. В результате, как и в парафазной схеме ЗУПВ, удается совместить во времени фазу записи  в

в  с фазой вывода

с фазой вывода  через последовательный порт вывода поток-инструкции

через последовательный порт вывода поток-инструкции  .

.

Такой режим работы  иллюстрирует табл. 5.2. В этом случае сигнал "чтение"

иллюстрирует табл. 5.2. В этом случае сигнал "чтение"  распространяется по бит-матрице не с задержкой на

распространяется по бит-матрице не с задержкой на  тактов, а с задержкой на 1 такт в каждой горизонтальной линейной цепочке слов-инструкций

тактов, а с задержкой на 1 такт в каждой горизонтальной линейной цепочке слов-инструкций  . Поэтому в соотношениях (5.1)-(5.5) надо использовать

. Поэтому в соотношениях (5.1)-(5.5) надо использовать  и

и  , а в соотношениях (5.4)-(5.5) фазовую задержку

, а в соотношениях (5.4)-(5.5) фазовую задержку  надо заменить на

надо заменить на  .

.

С системотехнических позиций порты рисунков 5.5 и 5.6 отличаются тем, что первый параметрически адаптируется под разрядность  , а второй - структурно, причем порту рис. 5.6 в традиционной вычислительной технике отвечает многопортовое ОЗУ прямого доступа, как по записи, так и по чтению.

, а второй - структурно, причем порту рис. 5.6 в традиционной вычислительной технике отвечает многопортовое ОЗУ прямого доступа, как по записи, так и по чтению.

а) выходы схем "И" кольцевых FIFO-регистров (  ) )

| |||||||

|---|---|---|---|---|---|---|---|

| Значение | 0 |  |

|

|

0 | ||

| Такт | 25 | 33 | 41 | 49 | 57 | ||

| Значение | 0 | 0 | 0 |  |

0 | ||

| Такт | 24 | 32 | 40 | 48 | 56 | ||

| Значение |  |

|

|

|

0 | ||

| Такт | 23 | 31 | 39 | 47 | 55 | ||

| Значение | 0 | 0 |  |

|

0 | ||

| Такт | 22 | 30 | 38 | 46 | 54 | ||

б) входы схемы "ИЛИ" порта вывода (  ) )

| |||||||

| Значение | 0 | 0 | 0 |  |

0 | ||

| Такт | 25 | 33 | 41 | 49 | 57 | ||

| Значение | 0 | 0 | 0 |  |

0 | ||

| Такт | 24 | 32 | 40 | 48 | 56 | ||

| Значение | 0 | 0 | 0 |  |

0 | ||

| Такт | 23 | 31 | 39 | 47 | 55 | ||

| Значение | 0 | 0 | 0 |  |

0 | ||

| Такт | 22 | 30 | 38 | 46 | 54 | ||

в) выходы линейной схемы "ИЛИ порта вывода (  ) )

| |||||||

| Значение | 0 | 0 | 0 |  |

0 | 0 | 0 |

| Такт | 27 | 35 | 43 | 51 | 59 | 67 | 75 |

| Значение | 0 | 0 | 0 |  |

|

0 | 0 |

| Такт | 26 | 34 | 42 | 50 | 58 | 66 | 74 |

| Значение | 0 | 0 | 0 |  |

|

|

0 |

| Такт | 25 | 33 | 41 | 49 | 57 | 65 | 73 |

| Значение | 0 | 0 | 0 |  |

|

|

|

| Такт | 24 | 32 | 40 | 48 | 56 | 64 | 72 |