|

Здравствуйте Владимир (Ефименко). Я обучаюсь по программе повышения квалификации "Наноэлектронная элементная база информатики на основе полупроводников и ферромагнетиков". У меня проблема с тестом № 2 (к лекции № 2) по этой программе. Я несколько раз пытался пройти этот тест, но больше 50 баллов набрать не удаётся, хотя я всё делаю в соответствии сматериалом лекции. В заданиях этого теста есть ошибки, которые видны невооружённым глазом. Обращаюсь к Вам как к инспектору этой программы повышения квалификации. Найдите возможность исправить ошибки в тесте № 2. Из-за остановки на этом тесте я не могу двигаться дальше, а у меня очень ограниченное время на освоение этой программы. Заранее благодарен Вам за внимание к моим проблемам и помощь. |

Одноэлектроника – одна из новых концепций построения НЭБИ

Одноэлектронные логические схемы

Как видим, ОЭТ является активным электронным элементом с довольно гибкими возможностями. Поэтому на основе ОЭТ можно строить логические схемы разного типа – потенциальные и импульсные, синхронные и асинхронные – с разными вариантами кодирования логических (двоичных) "0" и "1". Наиболее изученным сейчас и наиболее перспективным является вариант, похожий на хорошо известную логику на КМДП транзисторах (о них мы напомним в следующей лекции). Для этого используют описанные выше ОЭТ с двумя затворами. На один из них можно подать такое постоянное напряжение  , чтобы ОЭТ имитировал поведение КМДП транзистора

, чтобы ОЭТ имитировал поведение КМДП транзистора  -типа, т.е. закрывался в случае подачи на второй затвор положительного напряжения.

Первый затвор назовем затвором статуса, а второй – функциональным входом. В другом варианте на затвор статуса подают такое напряжение

-типа, т.е. закрывался в случае подачи на второй затвор положительного напряжения.

Первый затвор назовем затвором статуса, а второй – функциональным входом. В другом варианте на затвор статуса подают такое напряжение  , чтобы ОЭТ имитировал поведение КМДП транзистора

, чтобы ОЭТ имитировал поведение КМДП транзистора  -типа, т.е. открывался в случае подачи на второй затвор положительного напряжения.

-типа, т.е. открывался в случае подачи на второй затвор положительного напряжения.

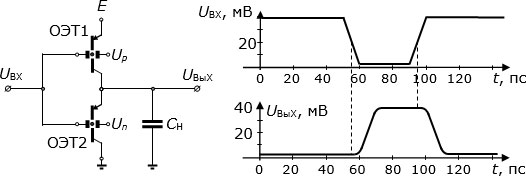

Схема соответствующего одноэлектронного инвертора показана на

рис.

4.5 слева. Транзистор ОЭТ1 имитирует поведение КМДП транзистора  -типа, а транзистор ОЭТ2 имитирует поведение КМДП транзистора

-типа, а транзистор ОЭТ2 имитирует поведение КМДП транзистора  -типа. Конденсатор

-типа. Конденсатор  – это эквивалент емкостной нагрузки на выход одноэлектронного инвертора. Когда на вход инвертора действует "высокий" положительный потенциал (близкий к напряжению питания

– это эквивалент емкостной нагрузки на выход одноэлектронного инвертора. Когда на вход инвертора действует "высокий" положительный потенциал (близкий к напряжению питания  ), который считаем сигналом логической "1", то транзистор ОЭТ1 закрывается, а ОЭТ2 – открывается. Падение напряжения между стоком и истоком открытого транзистора незначительное, поэтому на выходе устанавливается низкий потенциал.

), который считаем сигналом логической "1", то транзистор ОЭТ1 закрывается, а ОЭТ2 – открывается. Падение напряжения между стоком и истоком открытого транзистора незначительное, поэтому на выходе устанавливается низкий потенциал.

Рис. 4.5. Слева - принципиальная электрическая схема одноэлектронного инвертора. Справа - временные диаграммы сигналов на входе (сверху) и на выходе (снизу) одноэлектронного инвертора

Когда на входе инвертора потенциал низкий, то транзистор ОЭТ1 открыт, а ОЭТ2 – закрыт. На выходе устанавливается высокий потенциал, поскольку падение напряжения между стоком и истоком открытого транзистора ОЭТ1 незначительное. Справа на рис. 4.5 показаны временные диаграммы сигналов на входе и выходе инвертора.

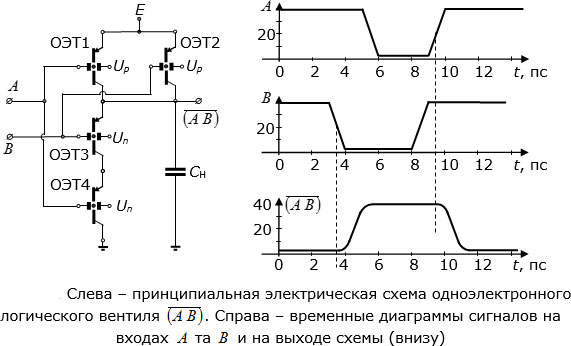

На

рис.

4.6 слева показана схема одноэлектронного логического вентиля отрицания конъюнкции  . Транзисторы ОЭТ1 и ОЭТ2 имитируют здесь поведение КМДП транзисторов

. Транзисторы ОЭТ1 и ОЭТ2 имитируют здесь поведение КМДП транзисторов  -типа, а транзисторы ОЭТ3 и ОЭТ4 – поведение КМДП транзисторов

-типа, а транзисторы ОЭТ3 и ОЭТ4 – поведение КМДП транзисторов  -типа. Конденсатор

-типа. Конденсатор  – эквивалент емкостной нагрузки на вентиль.

– эквивалент емкостной нагрузки на вентиль.

Обозначим

Когда потенциалы  и

и  и в соответствии с формулой (4.1) потенциал

и в соответствии с формулой (4.1) потенциал  , то уровень Ферми в области стока снижается на величину

, то уровень Ферми в области стока снижается на величину  , а энергетические уровни в квантовом наноостровке – на величину

, а энергетические уровни в квантовом наноостровке – на величину  . Энергетическая диаграмма на

рис.

4.4.б относится к случаю, когда

. Энергетическая диаграмма на

рис.

4.4.б относится к случаю, когда  . В этом случае на наноостровке нет разрешенного энергетического уровня, соответствующего уровню Ферми

. В этом случае на наноостровке нет разрешенного энергетического уровня, соответствующего уровню Ферми  . Поэтому туннельные переходы сквозь двойной туннельный барьер практически не происходят, и электрический ток стока близок к нулю. Транзистор закрыт.

. Поэтому туннельные переходы сквозь двойной туннельный барьер практически не происходят, и электрический ток стока близок к нулю. Транзистор закрыт.

Справа на

рис.

4.6 показаны временные диаграммы сигналов на входах  и

и  , которые специально несколько разнесены по времени поступления. Соответствующий сигнал на выходе схемы показан ниже. Он становится низким (логический "0") только тогда, когда на оба входа

, которые специально несколько разнесены по времени поступления. Соответствующий сигнал на выходе схемы показан ниже. Он становится низким (логический "0") только тогда, когда на оба входа  та

та  поданы сигналы логической "1".

поданы сигналы логической "1".

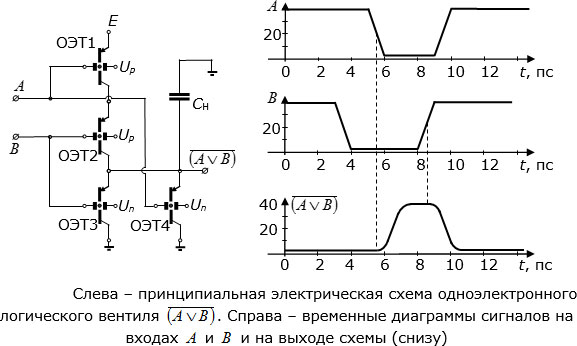

На

рис.

4.7 слева показана схема одноэлектронного логического вентиля отрицания дизъюнкции  .

.

Транзисторы ОЭТ1 и ОЭТ2 имитируют здесь поведение КМДП транзисторов  -типа, а транзисторы ОЭТ3 и ОЭТ4 –поведение КМДП транзисторов

-типа, а транзисторы ОЭТ3 и ОЭТ4 –поведение КМДП транзисторов  -типа. Конденсатор

-типа. Конденсатор  – эквивалент емкостной нагрузки на вентиль. Когда хотя бы на один из входов

– эквивалент емкостной нагрузки на вентиль. Когда хотя бы на один из входов  или

или  действует высокий потенциал (сигнал логической "1"), то хотя бы один из транзисторов ОЭТ1 или ОЭТ2 закрывается, а хотя бы один из транзисторов ОЭТ3 и ОЭТ4 открывается. На выходе устанавливается низкий потенциал. Когда на обоих входах потенциал низкий, то оба транзистора ОЭТ1 и ОЭТ2 открыты, а оба транзистора ОЭТ3 и ОЭТ4 – закрыты. На выходе устанавливается высокий потенциал. Таким образом, реализуется логическая функция отрицания дизъюнкции

действует высокий потенциал (сигнал логической "1"), то хотя бы один из транзисторов ОЭТ1 или ОЭТ2 закрывается, а хотя бы один из транзисторов ОЭТ3 и ОЭТ4 открывается. На выходе устанавливается низкий потенциал. Когда на обоих входах потенциал низкий, то оба транзистора ОЭТ1 и ОЭТ2 открыты, а оба транзистора ОЭТ3 и ОЭТ4 – закрыты. На выходе устанавливается высокий потенциал. Таким образом, реализуется логическая функция отрицания дизъюнкции  . В англоязычных источниках такую схему называют "NOR".

. В англоязычных источниках такую схему называют "NOR".

Справа на

рис.

4.7 показаны временные диаграммы сигналов на входах  и

и  , которые тоже специально несколько разнесены во времени, и соответствующие изменения сигнала на выходе схемы (внизу). Выходной сигнал становится высоким лишь тогда, когда на обоих входах

, которые тоже специально несколько разнесены во времени, и соответствующие изменения сигнала на выходе схемы (внизу). Выходной сигнал становится высоким лишь тогда, когда на обоих входах  и

и  действуют сигналы логического "0".

действуют сигналы логического "0".

С использованием описанных логических схем можно построить любую логику. При незначительных размерах ОЭТ плотность интеграции может быть очень высокой. Например, при размерах одного ОЭТ порядка 10 х 10 нм плотность интеграции может значительно превышать миллиард транзисторов на 1 мм2. И все они вместе будут потреблять мощность не больше 10 мВт.