|

Здравствуйте Владимир (Ефименко). Я обучаюсь по программе повышения квалификации "Наноэлектронная элементная база информатики на основе полупроводников и ферромагнетиков". У меня проблема с тестом № 2 (к лекции № 2) по этой программе. Я несколько раз пытался пройти этот тест, но больше 50 баллов набрать не удаётся, хотя я всё делаю в соответствии сматериалом лекции. В заданиях этого теста есть ошибки, которые видны невооружённым глазом. Обращаюсь к Вам как к инспектору этой программы повышения квалификации. Найдите возможность исправить ошибки в тесте № 2. Из-за остановки на этом тесте я не могу двигаться дальше, а у меня очень ограниченное время на освоение этой программы. Заранее благодарен Вам за внимание к моим проблемам и помощь. |

Наноэлектронная элементная база информатики на полупроводниках группы А_ІІІВ_V. Гетеротранзисторы

Введение

Для создания наноэлектронной элементной базы информатики используют не только кремний, но и другие полупроводники, в первую очередь, полупроводники группы  . Их основным преимуществом являются малая эффективная масса носителей электрического заряда и, соответственно, высокая подвижность этих носителей. Например, при температуре 300 К подвижность электронов проводимости в кремнии составляет приблизительно 0,15 м2/(В*с), а в

. Их основным преимуществом являются малая эффективная масса носителей электрического заряда и, соответственно, высокая подвижность этих носителей. Например, при температуре 300 К подвижность электронов проводимости в кремнии составляет приблизительно 0,15 м2/(В*с), а в  – 0,85 м2/(В*с), в

– 0,85 м2/(В*с), в  – 3,3 м2/(В*с), в

– 3,3 м2/(В*с), в  – 7,8 м2/(В*с). Поэтому элементы на таких полупроводниках имеют потенциально более высокое быстродействие.

– 7,8 м2/(В*с). Поэтому элементы на таких полупроводниках имеют потенциально более высокое быстродействие.

На "микроэлектронном" этапе развития элементной базы информатики приборы на арсениде галлия и других полупроводниках группы  все время опережали кремниевую электронику по быстродействию в несколько раз. Такое же соотношение между ними сохранилось и на "наноэлектронном" этапе развития.

все время опережали кремниевую электронику по быстродействию в несколько раз. Такое же соотношение между ними сохранилось и на "наноэлектронном" этапе развития.

Еще одним преимуществом полупроводников группы  является то, что большинство из них имеют схожую кристаллическую структуру и близкие значения периода кристаллической решетки и поэтому хорошо подходят для гетероэпитаксиального наращивания. Они легко смешиваются между собой, образуя кристаллы типа

является то, что большинство из них имеют схожую кристаллическую структуру и близкие значения периода кристаллической решетки и поэтому хорошо подходят для гетероэпитаксиального наращивания. Они легко смешиваются между собой, образуя кристаллы типа  ,

,  и т.п. Это позволяет получать полупроводниковые кристаллы с вариациями периода кристаллической решетки и с разной шириной запрещенной зоны энергий от 0,17 эВ в

и т.п. Это позволяет получать полупроводниковые кристаллы с вариациями периода кристаллической решетки и с разной шириной запрещенной зоны энергий от 0,17 эВ в  до 3,39 эВ – в

до 3,39 эВ – в  .

Ширина запрещенной зоны в чистом арсениде галлия 1,424 эВ (при 300 К) существенно больше, чем в кремнии (1,12 эВ), что позволяет приборам на арсениде галлия функционировать в значительно более широком диапазоне температур. Благодаря большей ширине запрещенной зоны чистый (или компенсированный) арсенид галлия имеет значительно более высокое удельное сопротивление. Поэтому для формирования интегральных схем можно использовать очень высокоомную подложку из арсенида галлия, функционирующую как изолятор, гальванически "развязывая" элементы микросхемы друг от друга.

.

Ширина запрещенной зоны в чистом арсениде галлия 1,424 эВ (при 300 К) существенно больше, чем в кремнии (1,12 эВ), что позволяет приборам на арсениде галлия функционировать в значительно более широком диапазоне температур. Благодаря большей ширине запрещенной зоны чистый (или компенсированный) арсенид галлия имеет значительно более высокое удельное сопротивление. Поэтому для формирования интегральных схем можно использовать очень высокоомную подложку из арсенида галлия, функционирующую как изолятор, гальванически "развязывая" элементы микросхемы друг от друга.

Однако имеются и существенные минусы. Как мы уже писали в лекции 5, кремний – это один из самых распространенных на Земле химических элементов и поэтому один из наиболее дешевых. Полупроводники группы  – намного более дорогие материалы. И вдобавок они не имеют такого естественного оксида, как

– намного более дорогие материалы. И вдобавок они не имеют такого естественного оксида, как  , из-за чего имеют обычно весьма высокую плотность поверхностных состояний. А это делает практически невозможным формирование на них КМДП транзисторов и значительно усложняет технологию производства.

, из-за чего имеют обычно весьма высокую плотность поверхностных состояний. А это делает практически невозможным формирование на них КМДП транзисторов и значительно усложняет технологию производства.

Полевые транзисторы с затвором Шоттки

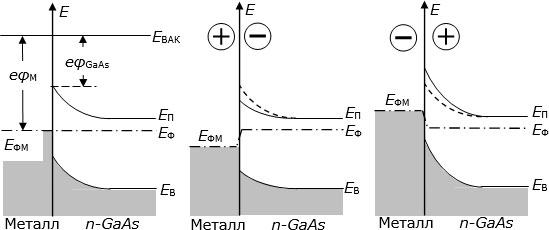

На "микроэлектронном" этапе развития одним из наиболее распространенных вариантов транзисторов на арсениде галлия были полевые транзисторы с затвором Шоттки (ПТЗШ). В англоязычной литературе их обычно называют MESFET (metal semiconductor field effect transistor). Здесь "metal semiconductor" упоминается потому, что барьер Шоттки как раз и возникает на контакте металла с полупроводником. На

рис.

8.1 слева показана энергетическая диаграмма контакта между металлом и полупроводником  -типа проводимости в типичном случае, когда работа выхода электронов из металла (

-типа проводимости в типичном случае, когда работа выхода электронов из металла ( ) больше работы выхода электронов из полупроводника (

) больше работы выхода электронов из полупроводника ( ). Именно такой вариант используют в работе ПТЗШ.

). Именно такой вариант используют в работе ПТЗШ.

Рис. 8.1. Энергетическая диаграмма контакта металла с полупроводником n-типа проводимости: слева – при отсутствии внешнего напряжения, в центре – при положительном напряжении на металлическом контакте; справа – при отрицательном напряжении

Вдоль вертикали здесь отложена потенциальная энергия электронов  , вдоль горизонтали – координата. Участки координаты, которые отвечают металлу и арсениду галлия

, вдоль горизонтали – координата. Участки координаты, которые отвечают металлу и арсениду галлия  -типа, соответственно подписаны. Обозначения:

-типа, соответственно подписаны. Обозначения:  – потенциальная энергия электронов в вакууме (вне металла и полупроводника);

– потенциальная энергия электронов в вакууме (вне металла и полупроводника);  – работа выхода электронов из металла и

– работа выхода электронов из металла и  – работа выхода электронов из полупроводника;

– работа выхода электронов из полупроводника;  и

и  – уровни Ферми электронов в металле и в полупроводнике;

– уровни Ферми электронов в металле и в полупроводнике;  и

и  – соответственно "потолок" валентной зоны и "дно" зоны проводимости.

Из-за того, что работа выхода электронов из металла

– соответственно "потолок" валентной зоны и "дно" зоны проводимости.

Из-за того, что работа выхода электронов из металла  больше

больше  , поток электронов из полупроводника в металл преобладает до тех пор, пока не установится такая контактная разность потенциалов (

, поток электронов из полупроводника в металл преобладает до тех пор, пока не установится такая контактная разность потенциалов ( , которая уравновешивает потоки электронов из металла в полупроводник и из полупроводника в металл. Эту равновесную разность потенциалов называют "барьером Шоттки". Возникновение контактной разности потенциалов приводит к искривлению вверх энергетических зон в полупроводнике в пространственной области, прилегающей к контакту с металлом. В этой области практически не остается электронов проводимости, поэтому ее называют "обедненной".

, которая уравновешивает потоки электронов из металла в полупроводник и из полупроводника в металл. Эту равновесную разность потенциалов называют "барьером Шоттки". Возникновение контактной разности потенциалов приводит к искривлению вверх энергетических зон в полупроводнике в пространственной области, прилегающей к контакту с металлом. В этой области практически не остается электронов проводимости, поэтому ее называют "обедненной".

Если на металлический электрод подать положительный электрический потенциал, то уровень Ферми  для электронов в металле снижается относительно уровня Ферми

для электронов в металле снижается относительно уровня Ферми  для электронов в полупроводнике. При этом искривление энергетических зон полупроводника возле контакта уменьшается и соответственно суживается область обеднения (

рис.

8.1 в центре).

Если на металлический электрод подать отрицательный потенциал, то уровень Ферми

для электронов в полупроводнике. При этом искривление энергетических зон полупроводника возле контакта уменьшается и соответственно суживается область обеднения (

рис.

8.1 в центре).

Если на металлический электрод подать отрицательный потенциал, то уровень Ферми  для электронов в металле поднимается над уровнем Ферми

для электронов в металле поднимается над уровнем Ферми  для электронов в полупроводнике, возрастает искривление энергетических зон полупроводника возле контакта и соответственно расширяется область обеднения (

рис.

8.1 справа). Для сравнения начальное положение дна зоны проводимости (в случае отсутствия напряжения смещения) показано штриховой линией.

для электронов в полупроводнике, возрастает искривление энергетических зон полупроводника возле контакта и соответственно расширяется область обеднения (

рис.

8.1 справа). Для сравнения начальное положение дна зоны проводимости (в случае отсутствия напряжения смещения) показано штриховой линией.

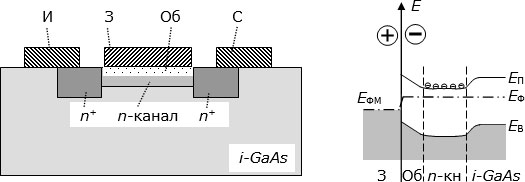

На рис. 8.2 слева показана типичная структура ПТЗШ.

На поверхности основы из высокоомного ("полуизолирующего") арсенида галлия ( ) с помощью ионной имплантации создан канал – тонкий слой

) с помощью ионной имплантации создан канал – тонкий слой  -типа проводимости с концентрацией электронов проводимости порядка 1023 м–3. Над ним сформирован электрод затвора (З), обычно из пленки золота. С помощью ионной имплантации сформированы более глубокие высоколегированные "карманы"

-типа проводимости с концентрацией электронов проводимости порядка 1023 м–3. Над ним сформирован электрод затвора (З), обычно из пленки золота. С помощью ионной имплантации сформированы более глубокие высоколегированные "карманы"  -типа проводимости, выполняющие функции истока и стока транзистора. Затем сформированы металлические омические контакты к ним (И и С).

-типа проводимости, выполняющие функции истока и стока транзистора. Затем сформированы металлические омические контакты к ним (И и С).

Когда напряжение между затвором и истоком мало (ниже порога открывания), обедненная область (Об) барьера Шоттки пронизывает весь слой п-типа проводимости. Поэтому его электрическое сопротивление очень велико, и сквозь транзистор электрический ток практически не протекает. Если между затвором и истоком подать электрическое напряжение выше порога открывания, то обедненная область (Об) суживается, и появляется узкий, не обедненный носителями слой –  -канал проводимости.

-канал проводимости.

Чем больше напряжение на затворе, тем шире этот канал, и тем больший по величине электрический ток течет сквозь транзистор. Положение порога открывания транзистора зависит от первоначальной толщины слоя  -типа проводимости: чем он толще, тем ниже лежит порог открывания.

-типа проводимости: чем он толще, тем ниже лежит порог открывания.

На

рис.

8.2 справа показана энергетическая диаграмма описанной структуры – зависимость потенциальной энергии электронов  от координаты вдоль перпендикуляра к плоскости электрода затвора. Внизу отмечены пространственные области затвора (З), обедненной области (Об), канала проводимости (

от координаты вдоль перпендикуляра к плоскости электрода затвора. Внизу отмечены пространственные области затвора (З), обедненной области (Об), канала проводимости ( -кн) и изолирующей подложки (

-кн) и изолирующей подложки ( ). Обозначения

). Обозначения  и

и  соответствуют уровням Ферми электронов в металле и в полупроводнике;

соответствуют уровням Ферми электронов в металле и в полупроводнике;  и

и  – "потолку" валентной зоны и "дну" зоны проводимости соответственно. Видно, что значительное количество электронов проводимости имеется лишь в канале, где образуется для них "потенциальная яма".

– "потолку" валентной зоны и "дну" зоны проводимости соответственно. Видно, что значительное количество электронов проводимости имеется лишь в канале, где образуется для них "потенциальная яма".

Базовая электрическая схема логического инвертора на таких транзисторах показана на рис. 8.3.а. Здесь UП – напряжение питания; И, З и С – исток, затвор и сток ПТЗШ; ТН – нагрузочный транзистор без затвора. Структура такого инвертора в кристалле арсенида галлия показана на рис. 8.3.б. Нагрузочный транзистор показан в разрезе справа. По структуре он такой же, как и ПТЗШ, но значительно yже и не имеет затвора. Соответственно в нем нет барьера Шоттки и области обеднения, так что он имеет постоянное электрическое сопротивление, которое в несколько раз превышает сопротивление открытого ПТЗШ, но во много раз меньше сопротивления закрытого ПТЗШ.

Входной сигнал подается на затвор инвертора. Если напряжение на входе низкое (логический "0"), то ПТЗШ закрыт, его электрическое сопротивление велико, и на выходе поддерживается высокое напряжение, близкое к напряжению питания (логическая "1"). Когда напряжение на входе высокое (логическая "1"), то ПТЗШ открыт, его электрическое сопротивление относительно мало, и на выходе устанавливается низкий потенциал (логический "0").

Типичная передаточная характеристика инвертора на ПТЗШ показана на рис. 8.3.в. А на рис. 8.3.г показана логическая схема NOR на ПТЗШ. У нее на выходе формируется сигнал логической "1" только тогда, когда на оба входа приходят сигналы логического "0".

Благодаря преимуществам арсенида галлия предельная частота ПТЗШ уже при проектно-технологических нормах 100-200 нм составляла 20-60 ГГц – в несколько раз выше, чем у МДП транзисторов на кремнии.

Для дальнейшего повышения быстродействия ПТЗШ необходимо, с одной стороны, уменьшать время пролета  -канала электронами проводимости, а с другой стороны, увеличивать электрический ток сквозь открытый транзистор, чтобы быстрее перезаряжать паразитные емкости межсоединений.

-канала электронами проводимости, а с другой стороны, увеличивать электрический ток сквозь открытый транзистор, чтобы быстрее перезаряжать паразитные емкости межсоединений.

Рис. 8.3. а) Базовая электрическая схема инвертора на ПТЗШ; б) структура кристалла с инвертором; в) типичная передаточная характеристика инвертора; г) логическая схема NOR

Но эти требования противоречивы. Для выполнения второго надо увеличивать электропроводность  -канала за счет увеличения концентрации донорных примесей. Но это приводит к увеличению частоты рассеяний электронов проводимости на примесях и соответственно – к росту времени пролета этих электронов сквозь канал. Образовался порочный "замкнутый круг", который препятствовал дальнейшему повышению быстродействия.

-канала за счет увеличения концентрации донорных примесей. Но это приводит к увеличению частоты рассеяний электронов проводимости на примесях и соответственно – к росту времени пролета этих электронов сквозь канал. Образовался порочный "замкнутый круг", который препятствовал дальнейшему повышению быстродействия.