Опубликован: 04.08.2025 | Доступ: свободный | Студентов: 13 / 0 | Длительность: 02:58:00

Лекция 1:

Введение в разработку цифровых ИС

Рынок полупроводниковых устройств

(* https://market.us/report/semiconductor-market/ (2024))

Некоторые отечественные разработчики и производители интегральных схем

История развития интегральных схем

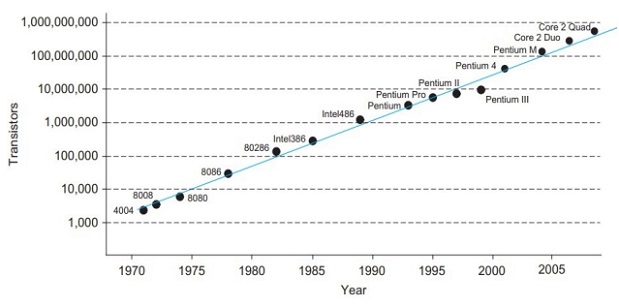

Закон Мура

Закон Мура (1965): удельное количество транзисторов на кристалле ИС удваивается примерно каждые 24 месяца.

Полный путь разработки ИС

Бюджет и планирование

- Описание архитектуры\микроархитектуры устройства

- Финансовое обеспечение проекта

- Не забудьте дополнительный запас по времени и средствам!

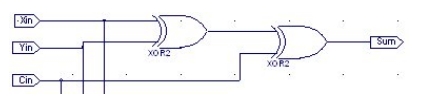

Схема и HDL описание

-

Основные методы описания цифрового устройства: схемный ИЛИ текстовый

-

Схема: - прост для начинающих - подходит только для небольших проектов

-

Текстовый: - используются языки описания аппаратуры (HDL) - похоже на программирование - удобен для описания больших проектов

RTL моделирование

- Компьютерное моделирование, позволяющее оценить работоспособность HDL описания

- Простейший способ - подача на вход схемы (описания на HDL) тестовых сигналов и сравнение выходных сигналов схемы с эталонными

- HDL описание, используемое для проверки корректной работы дизайна, называется "testbench" или "модуль тестовых воздействий"

- Моделирование проводится с помощью спец. ПО ("HDL симуляторы"), позволяющего также строить временные диаграммы сигналов (фактически - изменение переменных HDL описания "во времени")

Прототипирование и отладка на ПЛИС

- HDL описание (часто называется "RTL") с помощью специализированного ПО преобразовывается в т.н. "прошивку" для ПЛИС - конфигурируемых цифровых логических схем.

- ПЛИС, находящиеся на специальных отладочных платах, конфигурируются ("прошиваются") так, чтобы реализовать функциональность HDL описания.

- С помощью специального ПО (логические анализаторы) возможно наблюдать диаграммы сигналов внутри ПЛИС.

Логический синтез и временной анализ

- Исторически первые цифровые ИС были сделаны из простых логических элементов и проверялись на макетной плате вручную.

- Количество логических элементов росло -> необходимы способы автоматизации разработки и отладки > языки описания аппаратуры были разработаны для разработки и моделирования цифровых схем

- Verilog HDL и VHDL (1980-x) были одними из первых языков и в настоящее время широко распространены

- Это не программирование! Программы исполняются последовательно, когда как языки HDL описывают параллельные процессы, протекающие в цифровых схемах

N. B.! Некоторые конструкции языка несинтезируемы и используются только для моделирования