Разработка цифровых ИС на примере микроконтроллерного ядра SCR1 - топологическое проектирование

Полный путь разработки ИС

Логический синтез и временной анализ

- Для создания цифровой интегральной схемы необходимо преобразовать HDL описание в схему из логических ячеек (вентилей)

- Логический синтез - процесс преобразования HDL описания в текстовый список логических элементов (вентилей) и связей между ними - т.н. "нетлист (netlist)", выполняется с помощью спец. ПО - т.н. "синтезатор"

- Необходимые исходные данные: HDL описание дизайна, файлы пользовательских ограничений (т.н. "constraints"), библиотеки стандартных элементов

- Во время логического синтеза выполняется статический временной анализ (т.н. "STA") схемы - уточняется максимально достигнутая тактовая частота и отсутствие прочих нарушений (в частности, т.н. "нарушения установки\удержания" - hold/setup violations)

- Как правило, проводится совместно с логическим синтезом в том же самом ПО

- Файл пользовательских ограничений (т.н. ".sdc" файл) содержит информацию о желаемой максимальной тактовой частоте для данного дизайна, названия тактовых сигналов и.т.п.

- Результат успешного логического синтеза - "нетлист" (т.е. фактически схема дизайна для выбранной библиотеки стандартных логических элементов) без нарушений установки ("no setup violations")

Размещение и трассировка на кристалле

Размещение и трассировка на кристалле начинается непосредственно после успешного логического синтеза

Входные данные для размещения и трассировки на кристалле:

- "нетлист" (т.е. фактически схема дизайна для выбранной библиотеки стандартных логических элементов) без нарушений установки ("no setup violations"),

- файл пользовательских ограничений (.sdc файл, как правило, совпадает с таковым для логического синтеза)

- технологические библиотеки стандартных элементов

Во время топологического проектирования также выполняется статический временной анализ (т.н. "STA") схемы

В отличие от этапа логического синтеза (могут присутствовать нарушения удержания - hold violations), на этапе размещения и трассировки должны быть исправлены все временные нарушения. Как правило, исправление происходит автоматически самим ПО.

Размещение и трассировка на кристалле (т.н. PaR) - первый этап

Основные шаги PaR:

- построение плана кристалла, построение сети питания (floorplanning, power grid creation)

- размещение элементов на кристалле (placement)

- построение тактового дерева (clock tree synthesis)

- трассировка межсоединений (routing)

- финальные проверки (chip finishing)

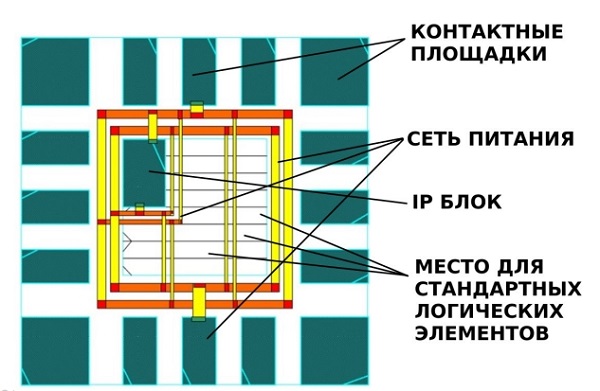

Построение плана кристалла, построение сети питания (floorplanning, power grid creation):

- определяются границы кристалла и его форма

- расставляются готовые топологические IP блоки (блоки памяти, IP блоки - ФАПЧ, и.т.п), их расположение фиксируется

- строится сеть питания, проверяется допустимое падение напряжения на проводниках (IR drop)

Результат этапа: предварительная компоновка кристалла ИС, используемые IP блоки (если используются) расставлены, создана сеть питания

* https://www.vlsiguru.com/floorplan-ppt-saurabh/

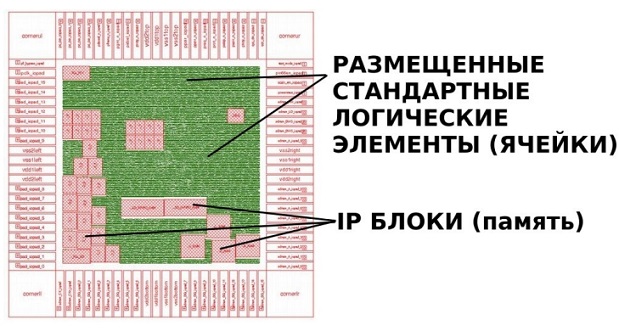

Размещение элементов на кристалле (placement):

- производится расстановка стандартных библиотечных элементов, использованных в нетлисте, на площади кристалла

- проводится оценка временных характеристик (максимальная тактовая частота) и проверка на отсутствие нарушений установки/удержания (setup/hold violations) с учетом полученного размещения стандартных элементов

Размещение элементов на кристалле (placement):

- как правило, расстановка проводится в два этапа - предварительное и точное размещение (coarse и fine).

- в процессе предварительного размещения элементы размещаются для определения "общей картины" (занимаемая площадь, возможность создать межсоединения - хватает ли количества слоёв, и.т.п)

- в процессе последующего точного размещения элементы расставляются строго в ряды (т.н. "placement rows"), их расположение фиксируется - дизайн "легализован" (т.н. "legalized placenement")

Размещение элементов на кристалле (placement):

- размещение элементов может выполняться с учетом временных ограничений (timing-driven placement) или с учетов возможностей для создания межсоединений (congestion-driven placement)

Результат этапа: кристалл с сеткой питания, IP блоками, размещенными и легализованным стандартными библиотечными элементами

Построение тактового дерева (clock tree synthesis):

- создаются проводники для тактирующих сигналов с учетом минимизации разброса по времени прихода тактирующего фронта (т.н. "clock skew")

- проводится оценка временных характеристик (максимальная тактовая частота) и проверка на отсутствие нарушений установки/удержания (setup/hold violations) с учетом "clock skew"

- тактовые цепи после этого этапа считаются реально существующими (т.н. "propagated")

Результат этапа: кристалл с сеткой питания, IP блоками, размещенными и легализованным стандартными библиотечными элементами, созданы тактовые проводники.

Трассировка межсоединений (routing):

- создаются проводники для сигнальных цепей согласно нетлисту, полученному на этапе логического синтеза

- проводится оценка временных характеристик (максимальная тактовая частота) и проверка на отсутствие нарушений установки/удержания (setup/hold violations)

Результат этапа: кристалл с сеткой питания, IP блоками, размещенными и легализованным стандартными библиотечными элементами, созданы тактовые и сигнальные проводники

Финальные проверки (chip finishing):

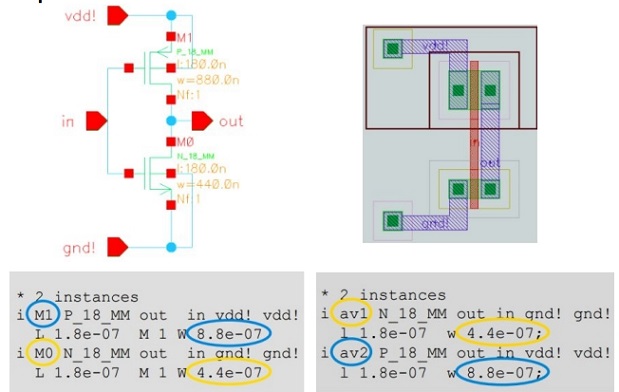

- проверка соответствия полученной топологии нетлисту (т.е. фактически схеме) - т.н. "layout vs schematic, LVS"

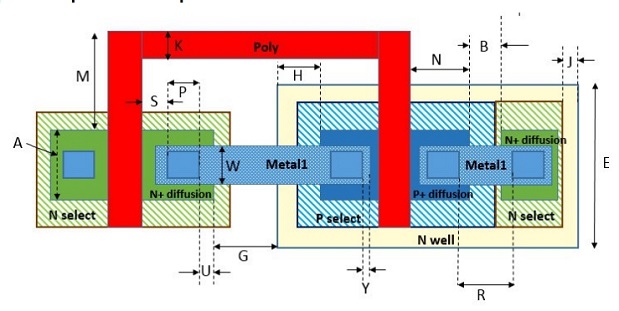

- проверка соответствия полученной топологии фабричным правилам проектирования для минимизации дефектов при изготовлении кристалла ИС - т.н. "design rule check, DRC"

- финальные проверки временных характеристик - т.н. "sign-off STA"

Пример LVS анализа:

Пример DRC правил: