Опубликован: 04.08.2025 | Доступ: свободный | Студентов: 13 / 0 | Длительность: 02:58:00

Лекция 4:

Разработка цифровых ИС на примере микроконтроллерного ядра SCR1 - прототипирование на ПЛИС

Прототипирование и отладка на ПЛИС

- Один из обязательных шагов проектирования цифровых ИС

- HDL описание (часто называется "RTL") с помощью специализированного ПО преобразовывается в т.н. "прошивку" для ПЛИС - конфигурируемых цифровых логических схем.

- ПЛИС, находящиеся на специальных отладочных платах, конфигурируются ("прошиваются") так, чтобы реализовать функциональность HDL описания.

- С помощью специального ПО (логические анализаторы) возможно наблюдать диаграммы сигналов внутри ПЛИС

-

RTL код, портируемый на ПЛИС, должен быть синтезируемым, некоторые модули (память, clock gates, синхронизаторы) должны быть описаны:

- либо на поведенческом уровне HDL;

- либо должны использоваться примитивы из библиотеки ПЛИС, на который осуществляется портирование;

- Прототипирование на ПЛИС позволяет сократить время, затрачиваемое на отладку ПО (т.н. "FPGA-based SDK")

- Использование готовых IP блоков, предоставляемых производителями ПЛИС, позволяет гибко менять окружение прототипируемой ИС в зависимости от требуемой задачи

- Недостатки - сравнительно небольшие максимальные тактовые частоты проектов на ПЛИС, дороговизна отладочных плат с ПЛИС больших объемов, равно как и коммерческих лицензий на спец ПО для прототипирования на ПЛИС (Vivado, Quartus)

Обзор проектов на ПЛИС для SCR1:

-

Проект на ПЛИС для плат:

-

Digilent Arty (Xilinx)

- Terasic DE10-Lite (Intel)

- Arria V GX Starter (Intel)

- Digilent Nexys 4 DDR (Xilinx)

-

-

Требуемое ПО:

- Xilinx Vivado Design Suite WebPACK

- Minicom/TeraTerm - терминал

Репозиторий с проектами на ПЛИС для SCR1

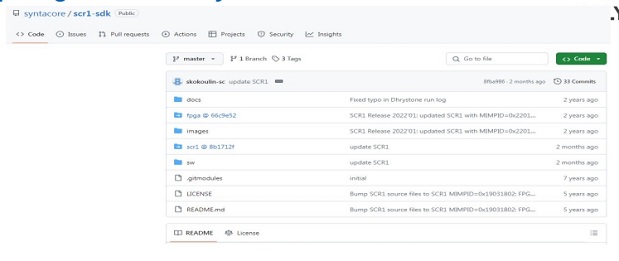

https://github.com/syntacore/scr1-sdk

Содержимое репозитория SCR1 FPGA SDK

- https://github.com/syntacore/scr1-sdk

-

SCR1 репозиторий содержит:

- docs <=== документация на проект для ПЛИС

- fpga <=== примеры проектов для ПЛИС

- images <=== готовые конфигурационные файлы для ПЛИС

- scr1 <=== RTL-описание ядра SCR1

- sw <=== ПО для проекта на ПЛИС

-

fpga каталог репозитория содержит:

- скрипты для помещения загрузчика во внутреннюю память ПЛИС

- дополнительные hex файлы для проекта на ПЛИС (Altera\Intel)

-

готовые для развертывания проекты для следующих отладочных плат с ПЛИС:

- Digilent Nexys A7 (Nexys 4 DDR

- Terasic DE10-Lite

-

Digilent Arty A7

- Arria V GX Starter 8

-

Проект для отладочной платы Arty содержит:

- Tcl скрипт для разворачивания проекта в Vivado (arty_scr1.tcl)

- Tcl скрипт для обновления памяти ПЛИС (mem_update.tcl & write_mmi.tcl)

- ПО загрузчика для ядра SCR1 в формате .mem (scbl.mem)

- файлы пользовательских ограничений для проекта на ПЛИС (constrs каталог)

- RTL исходники для проекта на ПЛИС (src каталог)