|

Здравствуйте Владимир (Ефименко). Я обучаюсь по программе повышения квалификации "Наноэлектронная элементная база информатики на основе полупроводников и ферромагнетиков". У меня проблема с тестом № 2 (к лекции № 2) по этой программе. Я несколько раз пытался пройти этот тест, но больше 50 баллов набрать не удаётся, хотя я всё делаю в соответствии сматериалом лекции. В заданиях этого теста есть ошибки, которые видны невооружённым глазом. Обращаюсь к Вам как к инспектору этой программы повышения квалификации. Найдите возможность исправить ошибки в тесте № 2. Из-за остановки на этом тесте я не могу двигаться дальше, а у меня очень ограниченное время на освоение этой программы. Заранее благодарен Вам за внимание к моим проблемам и помощь. |

Наноэлектронные устройства памяти на кремниевых КМДП транзисторах

Память на МДП транзисторах и элементах с изменением фазового состояния

Еще одним видом наноэлектронной памяти на МДП транзисторах, который интенсивно разрабатывают ведущие фирмы в последние годы, является память на элементах с изменением фазового состояния (далее ИФС; англ. рhase-change memory, РСМ). Этот вид памяти в англоязычных источниках называют также PRAM, PCRAM, Chalcogenide RAM, C-RAM.

Функционирование такой памяти основано на способности ряда материалов, в частности халькогенидного стекла, стабильно существовать при комнатных температурах как в стеклообразном (аморфном), так и в кристаллическом состоянии. В кристаллическом состоянии электрическое сопротивление такого материала относительно мало, тогда как в аморфном – на несколько порядков выше. А еще важно то, что такие материалы могут быстро переходить из одного состояния в другое при нагревании до определенной температуры, которое достигается пропусканием сквозь элемент ИФС дозированных импульсов электрического тока. Температура кристаллизации, как правило, значительно ниже температуры плавления, при которой материал переходит в аморфное состояние. При больших размерах элементов ИФС их переключение связано с довольно значительными затратами энергии. Но эти затраты очень быстро уменьшаются с уменьшением размеров. И при размерах порядка 30 нм и менее становятся совсем незначительными, так что требуемые токи могут уже обеспечиваться наноэлектронными МДП транзисторами.

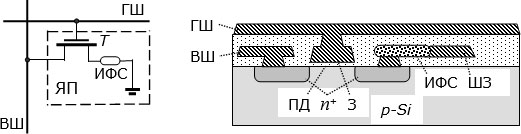

Схема ячейки памяти (ЯП) на элементе ИФС и ее подключение к горизонтальной (ГШ) и вертикальной (ВШ) шинам в матрице памяти показана на рис. 6.12 слева. МДП транзистор соединен с элементом ИФС последовательно и используется как ключ выборки. Его затвор соединяется с горизонтальной, а сток – с вертикальной шиной матрицы памяти.

Обычно горизонтальные шины играют роль адресных. Лишь на одну из них с дешифратора подается высокий потенциал. И в соответствующей строке матрицы открываются все ключевые транзисторы. Одна из вертикальных шин через периферийный ключевой транзистор соединяется с источником напряжения считывания. Величина электрического тока, протекающего при этом, зависит от состояния элемента ИФС. Если он находится в кристаллическом состоянии, то его сопротивление мало, и сквозь ячейку памяти и вертикальную шину протекает значительный электрический ток. Если же элемент ИФС находится в аморфном состоянии, то его сопротивление большое, и протекающий ток очень мал.

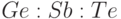

Рис. 6.12. Слева – схема ячейки памяти из МДП транзистора и элемента с изменением фазового состояния (ИФС). Справа – структура такой ячейки: ШЗ – шина "земли", общая для всех ячеек

В режиме побайтного считывания к источнику напряжения считывания через периферийные ключевые транзисторы присоединяются одновременно 8 вертикальных шин, а в режиме параллельного считывания – одновременно все вертикальные шины матрицы. И происходит одновременное формирование сигналов считывания с 8 или из всех ячеек памяти в выбранной строке.

Такой же порядок выборки ячеек памяти применяют и в режиме записи информации. Вот только присоединяются они не к источнику относительно низкого напряжения считывания, а к источнику соответствующих импульсов записи.

Структура ячейки памяти на элементах ИФС показана на

рис.

6.12 справа. Наноразмерные карманы  -типа в кремнии р-типа образуют исток и сток МДП транзистора и инвертированный канал проводимости. Над этим каналом сформированы тонкий слой подзатворного диэлектрика (ПД) и электрод затвора (З). В сечении показаны также горизонтальная шина (ГШ), к которой присоединены затворы всех транзисторов одной строки матрицы, вертикальная шина (ВШ) и шина "земли" (ШЗ), которые проходят перпендикулярно к плоскости сечения. Элемент ИФС включен между истоком транзистора и шиной "земли". Чтобы обеспечить нужную плотность электрического тока во время импульсов записи, элемент ИФС делают значительно уже, чем ширина канала транзистора.

-типа в кремнии р-типа образуют исток и сток МДП транзистора и инвертированный канал проводимости. Над этим каналом сформированы тонкий слой подзатворного диэлектрика (ПД) и электрод затвора (З). В сечении показаны также горизонтальная шина (ГШ), к которой присоединены затворы всех транзисторов одной строки матрицы, вертикальная шина (ВШ) и шина "земли" (ШЗ), которые проходят перпендикулярно к плоскости сечения. Элемент ИФС включен между истоком транзистора и шиной "земли". Чтобы обеспечить нужную плотность электрического тока во время импульсов записи, элемент ИФС делают значительно уже, чем ширина канала транзистора.

В элементах ИФС, сформированных из халькогенидного стекла  в соотношении 2:2:5 с проектно-технологической нормой 90 нм время записи составляет порядка 100 нс. Оценки показывают, что при ПТН 20 нм время записи может быть сокращено до 5 нс.

в соотношении 2:2:5 с проектно-технологической нормой 90 нм время записи составляет порядка 100 нс. Оценки показывают, что при ПТН 20 нм время записи может быть сокращено до 5 нс.

Количество циклов гарантированной перезаписи в элементах ИФС оценивается в 100 млн. (в 1000 раз больше, чем в стандартной флеш-памяти), а время гарантированного хранения информации при рабочей температуре  оценивается в 300 лет.

оценивается в 300 лет.

Площадь ячеек памяти на элементах ИФС больше, чем площадь элементов флеш-памяти. Поэтому и себестоимость одного мегабита ИФС памяти выше себестоимости флеш-памяти. В связи с этим область применения памяти на элементах ИФС yже: они применяются пока что в основном в спецтехнике – там, где нужна повышенная радиационная стойкость. По этому показателю ИФС память превосходит флеш-память на порядки величины. Наноэлектронную ИФС память применяют и там, где нужна высокая скорость записи, а также гарантированное количество циклов перезаписи свыше 10 млн.

По состоянию на 2011 г. был освоен промышленный выпуск наноэлектронных кристаллов памяти на элементах ИФС объемом 512 Мбит.

Наноэлектронные ПЛИС на КМДП транзисторах

Ячейки энергонезависимой памяти на КМДП транзисторах с успехом используют также в программируемых логических интегральных схемах (ПЛИС, англ. programmable logic device, PLD). В отличие от серийных микропроцессоров, микроконтроллеров и других обычных цифровых интегральных схем, логика работы ПЛИС не определяется целиком при изготовлении, а задается самим пользователем, исходя из его конкретных задач. ПЛИС'ы применяют там, где нужна довольно сложная, но специфическая обработка информации, когда соответствующее оборудование выпускается относительно небольшими сериями. Если оборудование выпускается небольшими партиями, например, только тысячами или десятками тысяч штук, то заказ и изготовление специфических для него больших интегральных схем оказываются весьма дорогими. И к тому же обычно имеется большая вероятность того, что на каком-то этапе испытаний или эксплуатации оборудования появится необходимость несколько изменить логику работы. Тогда изготовление заказных интегральных схем становится еще более невыгодным экономически. В таких случаях экономически значительно целесообразнее использовать ПЛИС'ы, которые позволяют довольно просто вносить нужные изменения в логику работы оборудования. ПЛИС'ы широко используют также для перекодировки данных в системах, где необходимо организовать эффективное взаимодействие устройств, работающих в разных стандартах представления информации. Они нужны и для построения разнообразных адаптивных систем, меняющих логику своей работы в зависимости от изменения условий функционирования.

Применение матриц энергонезависимой памяти для построения ПЛИС основано на том, что такую матрицу можно рассматривать и использовать также и как логическую схему, в которой каждый разряд выходного двоичного кода является логической функцией от значений разрядов входного двоичного кода адреса. Нацеленно изменяя состояние ячеек памяти, можно запрограммировать требуемые логические функции любого уровня сложности.

Матрицу энергонезависимой памяти можно рассматривать и использовать также и как программируемый коммутатор, который позволяет нужным образом соединить горизонтальные шины с вертикальными для передачи сигналов от одних источников только на определенные другие.

Наноэлектронные ПЛИС разного уровня сложности выпускают в виде расположенных на одном кристалле:

- набора матриц памяти / логики,

- набора периферийных схем,

- регистров,

- дешифраторов,

- программированных коммутационных матриц,

- тактовых генераторов,

- программируемых таймеров,

- иногда сумматоров и схем умножения/деления,

которые формируются в ходе общего КМДП технологического процесса и допускают дальнейшее индивидуальное программирование. Их выпускают большими (миллионными и выше) тиражами, благодаря чему они остаются относительно дешевыми. А заносит информацию в них, "программирует" их, т.е. настраивает на выполнение тех или иных логических функций сам пользователь – в соответствии со стоящими перед ним задачами.

Производители ПЛИС обычно разрабатывают и продают также специальные пакеты программ для автоматизированного проектирования и программирования выпускаемых ими микросхем. Эти пакеты ("САПР" – системы автоматизированного проектирования) позволяют проводить проектирование, имитацию работы и тестирование спроектированных ПЛИС в относительно короткие сроки.

Переход к нанометровым размерам ячеек памяти открыл для ПЛИС "новое дыхание", так как сделал возможной реализацию на одном небольшом кристалле ПЛИС очень сложных специфических контроллеров, процессоров, блоков перекодировки информации, перерасчета ее в разные "базисы", коммутаторов, цифровых фильтров и т.п. с использованием уже миллионов доступных для записи и перезаписи ячеек памяти, т.е. миллионов эквивалентных логических вентилей, работающих на частотах в сотни мегагерц с низким уровнем энергопотребления.

Наноэлектронные ПЛИС'ы стали одной из наилучших элементных баз для реализации сложных нейронных сетей. Ведь на одном кристалле стало возможным моделировать работу тысяч параллельно функционирующих нейронов, обмен данными между которыми происходит в пределах одного кристалла с высокими скоростями.