|

Добрый день!

Скажите, пожалуйста,планируется ли продолжение курсов по нанотехнологиям? Спасибо, Евгений

|

Методы и средства обеспечения живучести и восстановления работоспособности МКМД-бит-потоковых субпроцессоров

Если на снижение размерности диагностируемого пространства основное влияние оказывают системотехнические факторы, то на снижение времени каждого проводимого теста - схемотехнические факторы, от которых зависит длина последовательности тест-данных. При этом топологическая схема тестового канала определяет продолжительность "сеанса связи" с каждым бит-процессором и поэтому разбивает "идеальную" тестовую последовательность на подпоследовательности, суммарная длина которых превосходит идеальную (см. раздел 7.4). Она формируется исходя из схемотехнических особенностей реализации бит-процессоров по методике восходящего синтеза (см. раздел 3.4) и поддерживается инструментальной платформой BPBrowse (см. раздел 6.4).

Бит-процессор может работать в трех режимах: комбинационного ( AND, NAND, XOR ), конечного ( ADD, ST1 ) и коммутационного ( WTR ) автомата с последовательным типом распространения данных в процессе передачи или обработки.

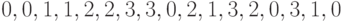

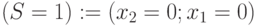

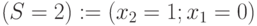

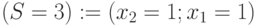

В режиме конечного автомата глубина обратной связи АЛУ (см. рис. 5.12 и 5.13 курса "Задачи и модели вычислительных наноструктур") равна одному такту. Поэтому минимальная последовательность тест-данных, в которой формируется декартово произведение второго порядка  , отвечающее полной матрице переходов такого автомата, имеет вид:

, отвечающее полной матрице переходов такого автомата, имеет вид:  .

.

Здесь  - десятичное представление наборов значений двоичных входных переменных бит-процессора:

- десятичное представление наборов значений двоичных входных переменных бит-процессора:  ,

,  ,

,  ,

,  .

.

Действующая карта отказов способна перевести бит-процессор из режима комбинационного в режим конечного автомата, что вынуждает использовать эту же последовательность и при диагностике "комбинационных" бит-инструкций.

При работе в режиме коммутационного автомата используются только D -триггеры канала АЛУ и транзита.

Полная матрица переходов этих триггеров задана на алфавите  и формируется последовательностью 00110.

и формируется последовательностью 00110.

Таким образом, при синтезе тестовых последовательностей проверяемые бит-процессоры приходится рассматривать как конечные, а не как комбинационные автоматы во всем пространстве их функциональных состояний.

Следовательно, снижение размерности задачи диагностики бит-матрицы и времени ее решения может быть достигнуто в основном за счет комплексного совмещенного во времени и пространстве контроля системы внутренней коммутации бит-процессора, которое обеспечивается:

- согласованным выбором в разных тестах направлений приема-передачи данных по трем независимым параллельным каналам их распространения через бит-процессор (всего 213 вариантов состояния внутренней системы коммутации);

- вариацией длины потока тест-данных

в зависимости от режима контроля бит-процессора, где основной вклад в полноту контроля вносят D -триггеры, если речь идет о проверке коммутационных возможностей бит-матрицы, и конвейерное суммирование, если речь идет о ее функциональном контроле.

в зависимости от режима контроля бит-процессора, где основной вклад в полноту контроля вносят D -триггеры, если речь идет о проверке коммутационных возможностей бит-матрицы, и конвейерное суммирование, если речь идет о ее функциональном контроле.

Таким образом, только комплекс схемо- и системотехнических мер с достоверными и поддерживаемыми в производстве СБИС упрощающими гипотезами или допущениями призван кардинальным образом снизить время прямой диагностики бит-матриц большой размерности с тем, чтобы довести это время до требований (квази)реального масштаба времени. В результате нисходящая (последовательно сужающая) по функциям и координатам стратегия диагностики приняла следующий вид.

Этап 1. На этом этапе осуществляется контроль коммутационных возможностей бит-матрицы и косвенный контроль управления бит-процессорами, состоящий из двух взаимосвязанных фаз. В первой фазе осуществляется контроль начального состояния D -триггеров операционных каналов и каналов транзита во всей бит-матрице путем "прослушивания" канала без подачи на его вход тестовых данных. Во второй фазе контролируется доступность каждого бит-процессора по ортогональным FIFO -регистровым каналам приема-передачи данных. Здесь уже используются последовательности входных тест-данных и анализируется качество отклика каждого бит-процессора, принадлежащего отдельному тестовому каналу. В этой фазе используются два типа коммутационных тестовых микропрограмм (см. рис. 7.20) с установкой "признака задержки" сначала в "ноль", а затем в "единицу". Полученные отклики бит-процессоров анализируются, и ставится диагноз для ка ждого бит-процессора. Если не удается точно локализовать координату отказавшего бит-процессора, то проводится уточняющее тестирование для всех накопленных неоднозначностей в локализации координаты отказавшего бит-процессора, но уже в усеченном виде, то есть только для бит-процессоров, "подозреваемых" на неисправность.

Этап 2. На этом этапе проводится функциональный контроль исполнения бит-инструкций, причем он осуществляется в обязательном порядке только для самых "сложных" бит-инструкций ADD, ST1, XOR табл. 3.1. Контроль исполнения более простых бит-инструкций ( AND, NAND ) осуществляется по необходимости и только для тех бит-процессоров, где выявлена неправильная реализация функций ( ADD ) или ( ST1 ).

Эта стратегия фактически базируется на следующих "аксиомах транзитивности", учитывающих масштабы последствий уже обнаруженных отказов:

- Если бит-процессор недоступен по ортогональным коммутационным D -шинам, то невозможно проконтролировать его правильное функционирование.

- Если бит-процессор или подматрица недоступны для тестовых микропрограмм, то они тем более недоступны и для микропрограмм поток-операторов пользователя.

В ассоциативных МКМД-бит-потоковых вычислителях особое место занимают отказы установки начального состояния D -триггеров каналов АЛУ и транзита, которые могут быть "захвачены" и сохранены микро- и макро-"вихрями" в потоках данных. Но вероятность таких отказов D -триггеров слишком мала (меньше 1%), а в масштабе бит-процессора еще меньше, зато высока вероятность константной неисправности (см. табл. 3.16).

Таким образом, данная стратегия диагностики обладает следующими особенностями:

- исходит из ранга теста, который определяется по степени катастрофичности последствий обнаруживаемых им отказов;

- ориентирована на максимальную адаптацию топологии всех последующих тестов на основе информации, полученной на предыдущих шагах и фазах тестирования, что снижает количество циклов и продолжительность контроля всей бит-матрицы;

- допускает адаптивность тестов не только к обнаруженной карте отказов, но и к операционному ресурсу, затребованному активным поток-оператором.

В последнем случае топология тестов строится исходя из пространственного распределения по бит-матрице составляющих поток-оператор бит-инструкций.

Алгоритмические, топологические и конструктивно-технологические особенности построения и адаптации тестовых микропрограмм под действующую карту отказов составляют сложный комплекс системотехнических проблем, от успешного решения которых во многом зависит уровень (квази)реального масштаба времени в системе обеспечения отказоустойчивости МКМД-бит-потоковых субпроцессоров.

Критерий эффективности работы адаптивных алгоритмов генерации тестовых микропрограмм определяется следующими факторами:

- сложностью, а значит, и временем синтеза теста и анализа полученных на его основе откликов;

- полнотой покрытия тестовыми микропрограммами диагностируемых функций и бит-матрицы и достоверностью результатов диагностики. Использование традиционных алгоритмов нахождения наименьшего

пути между двумя точками [300] методом динамического программирования (ДП) и алгоритмов с различными стратегиями или условиями возврата плохо совместимы с темпом реального времени из-за их высокой вычислительной сложности, особенно для бит-матриц больших размеров.

При использовании ДП-алгоритмов в каждом цикле в определенном порядке проверяются все бит-процессоры матрицы, число которых равно  , где

, где  - размер проверяемой бит-матрицы. Для каждого бит-процессора матрицы (в общем виде) выполняется 1 операция сравнения и 2 - присваивания. Следовательно, сложность этого алгоритма -

- размер проверяемой бит-матрицы. Для каждого бит-процессора матрицы (в общем виде) выполняется 1 операция сравнения и 2 - присваивания. Следовательно, сложность этого алгоритма -  в рамках только одного типа теста и одного набора тест-данных.

в рамках только одного типа теста и одного набора тест-данных.

В алгоритме с возвратом перебираются все возможные в рекурсивной процедуре пути, количество которых составляет  . Следовательно, сложность этого алгоритма -

. Следовательно, сложность этого алгоритма -  , что также плохо совместимо с темпом реального времени при больших размерах бит-матриц.

, что также плохо совместимо с темпом реального времени при больших размерах бит-матриц.

Если во главу угла поставить требование темпа реального времени при проведении эксплуатационной диагностики МКМД-бит-потоковых субпроцессоров, то необходимо отказаться от использования в адаптивных тестах от процедур нахождения минимального пути обхода обнаруженных неисправностей. Это снижает полноту диагностики бит-матрицы и увеличивает "пессимизм" в оценке локального последействия обнаруженного отказа, но упрощает алгоритм поиска спрямленного пути при обходе обнаруженных неисправностей. В отличие от предыдущих алгоритмов, в этом случае осуществляется проверка впереди лежащих бит-процессоров, и топология тестовой микропрограммы деформируется в соответствии с фиксированной стратегией обхода, если встречена преграда. Сложность описанного алгоритма составляет  , а его недостатком является неоптимальность порождаемого пути, которая мало сказывается на продолжительности достаточно полного покрытия бит-матрицы тестовыми микропрограммами, если тестир

уемый канал образован бит-процессорами одной строки бит-матрицы ("однострочный тест"). В подтверждение сказанного на рис. 7.21 приведены графики роста вычислительной сложности рассмотренных алгоритмов в зависимости от размера матрицы.

, а его недостатком является неоптимальность порождаемого пути, которая мало сказывается на продолжительности достаточно полного покрытия бит-матрицы тестовыми микропрограммами, если тестир

уемый канал образован бит-процессорами одной строки бит-матрицы ("однострочный тест"). В подтверждение сказанного на рис. 7.21 приведены графики роста вычислительной сложности рассмотренных алгоритмов в зависимости от размера матрицы.

Как показал модельный эксперимент, прямой алгоритм генерации тестовых микропрограмм целесообразно применять, если карта отказов имеет менее 3% отказавших бит-процессоров. При превышении этого показателя появляются локальные области бит-матрицы с исправными, но признанными недоступными для диагностики бит-процессорами, которые также приходится идентифицировать как полностью отказавшие. В результате разрастаются локальные области неисправностей, в которые включаются все бит-процессоры, лежащие внутри двумерной фигуры произвольной геометрической формы, вид которой зависит от топологии "точечных".

В описанных условиях многострочные промышленные тесты с независимыми по каждому операнду каналами формирования тест-данных (см. рис. 7.12-7.4) оказались малоэффективными [299] в условиях эксплуатации, так как парирование такими микропрограммами обнаруженных отказов требует анализа возможных путей прохождения через ортогональные квадраты размером, кратным количеству строк в канале теста. В результате в десятки раз увеличивается время генерации теста для одного тестового канала, и в сотни раз - время покрытия тестами всей бит-матрицы. При этом падает коэффициент распараллеливания тестовых микропрограмм, так как уменьшается полезная тестируемая "площадь" в рамках одного тестового канала, что вынуждает увеличивать количество циклов тестирования. Поэтому для исключения из тестовой микропрограммы вспомогательных строк (столбцов), по которым распространяются тест-операнды, необходимо изменить топологическую структуру эксплуатационных тестов и перейти к однострочным тестам эксплуатационной диагностики рис. 7.22.

Принципиальное отличие тестовых микропрограмм эксплуатационной диагностики состоит в том, что в них только один операнд подается и распространяется по бит-матрице как независимый, а второй формируется за счет реакции последующего бит-процессора. Это усложняет процедуры анализа откликов и делает алгоритмы локализации и идентификации отказов рекурсивными по форме. Совокупность описанных приемов позволила создать тестовые каналы, состоящие только из одной строки (см. рис. 7.22).

На рис. 7.22 показаны каналы однострочных тестов ADD, ST1 и XOR. Для них по методике, изложенной в разделе 3.4, минимальные по длине тестовые последовательности подобраны следующим образом. Выбирается тестовая последовательность "независимого" операнда, и на схеме теста в матрице без отказов моделируется отклик, который используется далее как второй "рекурсивный" операнд. Далее на модели отдельного бит-процессора полным перебором пространства одного и двух одновременных отказов анализируются диагностические возможности и полнота подобранных тестовых последовательностей. На основе полученных данных для тестируемой функции и каждой тестовой последовательности вычисляется величина  минимум которой служит признаком конца поиска требуемой тестовой последовательности. Здесь

минимум которой служит признаком конца поиска требуемой тестовой последовательности. Здесь  - количество правильных реакций для всевозможных подмножеств карт, насчитывающих не более двух одновременных отказов элементов схемы.

- количество правильных реакций для всевозможных подмножеств карт, насчитывающих не более двух одновременных отказов элементов схемы.

При таком тестировании бит-матрицы обнаруженный неправильный отклик ставит под подозрение в неисправности от трех "эквидистантных" бит-процессоров (при тестировании коммутации) до всей строки теста (при тестировании функции "запоминание единицей"). Для устранения такой неоднозначности определения координаты отказавшего бит-процессора необходимо использовать совокупность горизонтально-вертикальных тестов (рис. 7.23), в которой сопоставляются результаты "горизонтального" и "вертикального" тестирования. Такой подход к однозначному определению координаты отказа особенно эффективен при плавной динамике нарастания карты отказов, что характерно для условий эксплуатации, но он требует совместного анализа результатов, полученных в разных тестах. Это делает алгоритмы функционального контроля глобально зависимыми, что опасно для проведения диагностики сверхбольших коллективов вычислителей с "большими" картами отказов.

Алгоритм генерации горизонтально-вертикальных тестов выполняется в следующей последовательности:

- Выбирать доступную сторону интерфейса бит-матрицы, наиболее удобную для тестирования горизонтальных или вертикальных каналов.

- Создать массив из доступных интерфейсных бит-процессоров.

- Создать канал доступа для каждого члена массива в рамках одного теста.

- Поочередно предоставить каждому члену массива право сделать шаг по прямому алгоритму и определить координаты бит-процессора для продолжения маршрута. Дописать в тестовую микропрограмму соответствующий терм, а в поток тест-данных и эталонных откликов соответствующую подпоследовательность.

- Повторять 4 до тех пор, пока ни один член массива уже не сможет сделать шаг.

В соответствии с этим алгоритмом подсистема идентификации и локализации отказов работает следующим образом. На начальном этапе запуска обрабатываются системные данные о доступности интерфейса связи с бит-матрицей (см. рис. 7.18) и на каждый доступный периферийный бит-процессор создается "объект" канала теста, который сохраняется по указателю в массиве доступных бит-процессоров. Таких массивов всего четыре (для каждой стороны бит-матрицы). Предшествующая карта отказов регистрируется подсистемой локализации как исходная.

Далее на основе полученных исходных данных о доступном интерфейсе и существующей карты отказов выполняется контроль периферийных бит-процессоров, обеспечивающих интерфейс обмена с внешней средой. Если заданный пользователем процент периферийных бит-процессоров оказывается неисправным, то делается вывод, что вся бит-матрица на плате недоступна для тестирования.

После проверки интерфейса задается конфигурация бит-матрицы, доступная для проведения теста. Данная проверка осуществляется на основе предшествующей карты отказов с помощью рекурсивной процедуры типа "заливка", что применяется при редактировании рисунков. Если после "заливки" бит-матрицы существуют "белые пятна" (отказы бит-процессоров, образующие окружности и т. п.), то эти области помечаются как отказавшие.

Далее осуществляется сплошное покрытие тестами всего тела бит-матрицы, сначала горизонтальными, а затем вертикальными. После каждого цикла горизонтально-вертикального тестирования осуществляется анализ откликов, причем этот анализ зависит от типа теста.

Общим для всех процедур тестирования является последовательность их проведения, в которой первым шагом которых служит "прослушивание" канала теста без подачи тест-данных. "Прослушивание" призвано обнаружить неисправности D -триггеров типа "тождественной единицы" в каналах распространения откликов бит-процессоров. Этот этап по продолжительности обычно чуть больше или равен количеству термов в этом тестовом канале. Далее осуществляется анализ откликов на подаваемые тест данные. Здесь тесты разбиты на две категории. Первая категория тестов ( WTR, ADD, XOR ) основана на анализе откликов на одиночную тестовую последовательность, которая трансформируется в тестовую комбинацию в процессе распространения по бит-матрице (на рис. 7.22-а и 7.22-в - это последовательности "независимых" операндов без скобок).

Вторая категория тестов ( ST1, AND, NAND ) основана на анализе откликов на многократную тестовую последовательность, которая сначала доходит до последнего терма тестового канала и, разблокировав процедуру формирования второго операнда, перемещается к началу теста. В этом случае второй тестовый операнд для последующего бит-процессора одновременно является откликом предыдущего бит-процессора (на рис. 7.22-б - это последовательность "независимых" операндов в скобках). На основе таких тестов в качестве неисправных приходится помечать все бит-процессоры, принадлежащие одному тестовому каналу, что сильно усложняет контроль уже при карте отказов, содержащей свыше 1% отказавших бит-процессоров в матрице.

Каждый из тестов второй категории порождает только гипотезу о координатах отказавших бит-процессоров. Окончательно идентифицировать координату отказавшего бит-процессора можно только по пересечению гипотетических линий вертикальных и горизонтальных тестов с последующим индивидуальным тестированием подозреваемого бит-процессора. Если предположение подтверждается, то этот бит-процессор помечается как неисправный и далее игнорируется всеми последующими тестами.

Контроль доступного интерфейса повторяется после каждого цикла тестирования, но уже с учетом найденных неисправностей, а циклы тестирования повторяются до тех пор, пока не будут проконтролированы все коммутационно доступные бит-процессоры.

Набор термов для каждого теста хранится в виде констант внутри программы их генерации, и он активизируется в зависимости от направления прокладываемого пути.

Приведенные данные позволяют сделать следующие выводы:

- алгоритм синтеза тестовых микропрограмм носит тривиальный характер рекуррентного наращивания термов до вертикальных и/или горизонтальных размеров бит-матрицы;

- алгоритм анализа откликов также сводится к простой процедуре определения разницы между реальной последовательности и эталонной реакциями;

- однозначно идентифицировать координату отказа в рамках одного вертикального или горизонтального теста невозможно из-за эквидистантных по отношению к тестовому выходу бит-процессора [299], неисправность которых проявляется одинаково.

Основные сложности функционального эксплуатационного контроля возникают при наличии карт отказов, разрушающих регулярные структуры тестовых микропрограмм и получаемых с их помощью откликов бит-процессоров. Поэтому эффективность всей системы локализации и идентификации отказов в бит-матрице в основном определяется скоростью адаптации рассмотренных линейных тестов и порождаемых ими последовательностей откликов на действующую карту отказов.