|

Добрый день!

Скажите, пожалуйста,планируется ли продолжение курсов по нанотехнологиям? Спасибо, Евгений

|

Специфика построения аппаратных платформ высокопроизводительных вычислительных систем с микропрограммным уровнем доступа

3.4. Синтез ассоциативно управляемых МКМД-бит-потоковых матричных СБИС арифметико-логической обработки данных по критерию максимума отказоустойчивости

Изготовление СБИС - это сложный технологический процесс, состоящий из ряда этапов, каждый из которых должен завершаться контролем выходного продукта. При этом инструментальными методами контролируются параметры, а с помощью тестовой диагностики - работоспособность СБИС. Поэтому функциональный контроль СБИС в ходе ее изготовления является неотъемлемой частью технологического процесса, а длительность такого контроля в условиях массового производства СБИС считается одной из важнейших характеристик этого процесса, во многом определяющей производительность предприятия и экономичность производства.

Таким образом, увеличение масштабов производства и применения СБИС, а также высокая стоимость их изготовления ужесточают противоречивые требования к качеству и продолжительности диагностики современных вычислительных устройств. Именно это обстоятельство делает сходными проблемы проектной, промышленной и эксплуатационной диагностики программируемых изделий вычислительной техники, что вынуждает развивать интегрированный подход к созданию систем обеспечения живучести (Б)ВС.

Суть этого подхода сводится к построению иерархической системы согласованных тестов, наиболее полно и достоверно обеспечивающей контроль в течение всего жизненного цикла разработки (верификация проекта), изготовления (отбраковка негодных изделий) и использования (обнаружение, локализация и парирование множественных карт отказов) сложных изделий вычислительной техники, содержащих сотни миллионов активных компонент (транзисторов или вентилей).

Очевидно, что в современных (Б)ВС неделимой единицей диагностического проекта может быть только СБИС или УБИС. Эти изделия микроэлектроники сами по себе представляют достаточно сложные объекты диагностики, что требует использования внешних инструментальных ЭВМ, обеспечивающих верификацию проекта, отбраковку негодных изделий, а также обнаружение, локализацию и парирование множественных карт отказов в процессе эксплуатации и боевого применения (Б) ВС. При этом методы построения тестов должны учитывать ограничения вычислительных ресурсов инструментальных ЭВМ, находящихся в распоряжении разработчика, изготовителя или эксплуатирующего персонала.

Анализ особенностей диагностики СБИС при их проектировании, изготовлении и эксплуатации показывает [292-295], что задачи построения тестов, используемых на различных этапах, отличаются в основном только требуемой достоверностью результатов диагностики и составом множества контрольных точек, которые можно использовать при диагностике на каждом жизненном цикле создания и использования СБИС. Очевидно, что состав контрольных точек сокращается при переходе от проектирования к производству и далее к эксплуатации, что усложняет задачу локализации и идентификации отказов.

В связи с этим в [292] сформулирована общая задача построения проверяющих тестов для проектной и промышленной диагностики СБИС и предложен метод декомпозиции при построении проверяющих тестов, сущность которого заключается в расчленении схемы СБИС на независимые, обычно функционально интерпретируемые, подсхемы. Далее, исходя из доступных вычислительных возможностей, подсхемы расчленяют на конечно-автоматные и комбинационные блоки, для которых строят входные тестовые последовательности таким образом, чтобы обеспечивалась заданная достоверность диагностики.

Для МКМД-бит-процессорных матриц метод декомпозиции позволяет построить иерархическую схему объектов диагностики (рис. 3.20). Дальнейшее разбиение выделенных подсхем на конечно-автоматные и комбинационные блоки теряет смысл, так как только комплексное исследование всей схемы в целом позволяет увидеть полную картину протекающих в схеме процессов.

Чтобы обеспечить преемственность между системами промышленной и эксплуатационной диагностики, схему структурной декомпозиции аппаратных блоков и устройств рис. 3.20 необходимо дополнить сверху схемой функциональной декомпозиции МКМД-бит-потокового (суб)процессорного тракта, в состав которой входят следующие элементы: функциональные модули (поток-операторы), составляющие тракт; операционные модули (слов-инструкции), реализующие функции устройств управления, адресных, интерфейсных, операционных и диагностических устройств, составляющих поток-оператор; термы (элементарные строительные блоки), составляющие слов-инструкции; бит-процессоры, составляющие терм ; регистры команд, схема коммутации, АЛУ бит-процессора; логические схемы операционного базиса.

В качестве термов может выступать совокупность бит-процессоров, образующих ячейку систолической структуры, как это имеет место в конвейерном умножителе рис. 3.8, где две пары бит-процессоров образуют две ячейки систолической структуры с двумя входами-выходами каждая.

Только в такой многоуровневой системе диагностики становится возможным:

- на каждом уровне иерархии корректно выделить ядро объекта, контролируемое прямыми методами диагностики, и создать систему достоверных логических правил и выводов, распространяющих результаты прямого контроля на непроконтролированные части "сложного" объекта диагностики и его состояний;

- создать иерархическую систему преемственного порождения потоков тест-данных и оценки полноты и достоверности результатов контроля.

Первая специфическая особенность диагностики МКМД-бит-потоковых субпроцессоров состоит в том, что схема их функционально интерпретируемой декомпозиции изменяется в зависимости от их назначения даже при фиксированной структуре бит-матричной СБИС, а это делает алгоритмически зависимыми и тесты контроля реализуемых поток-операторов. Максимум что можно сделать в такой ситуации, это зафиксировать библиотеки термов и слов-инструкций и соответствующие им тесты обнаружения отказов.

Вторая специфическая особенность диагностики МКМД-бит-процессорной матрицы состоит в том, что ни один из составляющих ее бит-процессоров не является полнодоступным по входам-выходам. Это вынуждает генерировать не только тест-данные, но и синтезировать тестовые микропрограммы специальной топологии, обеспечивающие опосредованный доступ к "внутренним" бит-процессорам матрицы.

Предлагаемая методика многоуровневого имитационного моделирования МКМД-бит-потоковых субпроцессорных трактов исходит из того, что на каждом уровне иерархии определяется влияние отказов на работоспособность модулей этого уровня. И так, постепенно поднимаясь с уровня на уровень, оценивается общая отказоустойчивость МКМД-бит-потокового (суб)процессорного тракта.

Несмотря на кажущуюся простоту методики, основная сложность ее реализации связана с необходимостью анализа множества всевозможных карт отказов начиная с бит-процессорного уровня. Суммарное количество карт от 1 до  одновременных отказов логических вентилей,

одновременных отказов логических вентилей,  , определяется следующим выражением:

, определяется следующим выражением:

где  - количество логических вентилей в схеме;

- количество логических вентилей в схеме;  - количество карт отказов для

- количество карт отказов для  одновременных отказов;

одновременных отказов;  - число сочетаний из

- число сочетаний из  элементов по

элементов по  , а

, а  - количество возможных типов отказов одного вентиля.

- количество возможных типов отказов одного вентиля.

При этом необходимо оценить влияние каждой карты отказов на правильность реализации каждой бит-инструкции (в СБИС Н1841 ВФ1 таких инструкций 7).

Необходимость моделирования всех карт отказов вызвана тремя обстоятельствами:

- при активном противодействии с использованием оружия направленной энергии любая карта отказов может возникнуть не только в бит-матрице, но и в любом бит-процессоре;

- получить численную оценку появления катастрофической карты отказов для каждой бит-инструкции (в СБИС Н1841 ВФ1 всего 216 возможных инструкций) достаточно сложно из-за больших вариаций состава вентилей, принимающих участие в реализации каждой бит-инструкции;

- парирование карт отказов в бит-матрице методом переразмещения на ней микропрограммы поток-оператора требует знания остаточных функциональных и коммутационных возможностей неисправных бит-процессоров.

В таких условиях в технике прибегают к имитационному моделированию [292, 293], с помощью которого удается получить не строгие, но, тем не менее, достаточно достоверные инженерные оценки появления катастрофических карт отказов на ограниченном подмножестве проконтролированных карт отказов. Такие инженерные оценки необходимы для управления процессом разработки СБИС в диагностической плоскости проекта.

Но даже и в этом случае задача построения тестов и оценки их качества остается достаточно сложной, так как прототип катастрофической карты отказов для каждой бит-инструкции заранее неизвестен, что вынуждает решать задачу поиска таких тестов перебором, полнота и достоверность которого также нуждается в оценке.

При поиске минимальных тестовых последовательностей для логических блоков использовались следующие критерии останова процедур поиска.

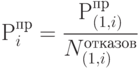

- Сгенерированная тестовая последовательность при контроле логического блока максимально покрывает пространство отказов этого блока, если величина

этого теста не может быть уже более понижена любым другим тестом. Такую последовательность будем называть полным тестом.

этого теста не может быть уже более понижена любым другим тестом. Такую последовательность будем называть полным тестом. - Если величина

полного теста с уменьшением его длины только увеличивается, то такой тест считается минимальным. Здесь- вероятность правильной реакции выхода схемы на входные воздействия,

полного теста с уменьшением его длины только увеличивается, то такой тест считается минимальным. Здесь- вероятность правильной реакции выхода схемы на входные воздействия,

( 1,i)})  . - количество правильных реакций при переборе всех

. - количество правильных реакций при переборе всех  карт отказов,

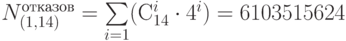

карт отказов,  - количество одновременных отказов, на котором процедура перебора останавливается. Для схем, имеющих не более 14 логических элементов (триггеры, мультиплексоры, дешифраторы),

- количество одновременных отказов, на котором процедура перебора останавливается. Для схем, имеющих не более 14 логических элементов (триггеры, мультиплексоры, дешифраторы),  приравнивается к количеству вентилей в схеме, то есть моделируются все возможные карты отказов, количество которых для 14 вентилей составит, согласно (3.4),

приравнивается к количеству вентилей в схеме, то есть моделируются все возможные карты отказов, количество которых для 14 вентилей составит, согласно (3.4),  вариантов.

(Время моделирования для 4-входовой схемы с 16-разрядными входными операндами составило около 22 часов для процессора Pentium-IV с тактовой частотой 1,5 ГГц.)

вариантов.

(Время моделирования для 4-входовой схемы с 16-разрядными входными операндами составило около 22 часов для процессора Pentium-IV с тактовой частотой 1,5 ГГц.)

Для схем, имеющих более 14 логических элементов, моделирование с использованием такого процессора удается провести полным перебором карт отказов, содержащих всего от 1 до 3 одновременно отказавших логических элементов. Например, для бит-процессора с 386 логическими элементами полный перебор для 1 и 2 одновременных карт отказов, согласно (3.4), составляет 1190424 вариантов, а время моделирования вышеуказанным процессором составило 50 минут.

Для построения и выбора иерархически преемственной системы тестов контроля аппаратной части МКМД-бит-потоковых субпроцессоров использовалось специально разработанное инструментальное средство Otkaz Modulate.exe. На его основе можно провести анализ влияния различных карт отказов вентилей на поведение известной моделируемой схемы и оценить диагностопригодность конкретного варианта тестовой последовательности. С этой целью в процессе анализа необходимо определить количество правильных реакций

(  ) для всевозможных подмножеств карт, насчитывающих от 1 до

) для всевозможных подмножеств карт, насчитывающих от 1 до  одновременных отказов элементов схемы. Мощность множества всевозможных подмножеств карт отказов равна

одновременных отказов элементов схемы. Мощность множества всевозможных подмножеств карт отказов равна  . После этого можно вычислить

. После этого можно вычислить  для каждой тестовой последовательности и сделать вывод о ее диагностопригодности по критерию полноты обнаружения отказавших элементов схемы.

для каждой тестовой последовательности и сделать вывод о ее диагностопригодности по критерию полноты обнаружения отказавших элементов схемы.

На устойчивость к отказам БП и матриц на их основе решающее влияние оказывает как состав функциональных блоков БП и распределение вентилей между ними, так и коэффициент использования вентилей при настройке БП на одну из требуемых функций. Последнее определяется конкретной логической схемой соединения блоков и устройств, образующих сквозной тракт прохождения преобразуемых потоков данных через БП. Поэтому при синтезе логических схем БП по критерию максимума устойчивости к отказам в первую очередь необходимо выделить блоки и узлы, приводящие к катастрофическим отказам как отдельных БП, так и матриц на их основе.

В табл. 3.15 приведено распределение логических вентилей по основным функциональным блокам БП СБИС Н1841 ВФ1. Из данных этой таблицы видно, что 43,1 % от общего количества вентилей занимают 16-разрядные сдвиговые FIFO -регистры команды. При равномерном распределении отказов по бит-матрице это приводит к тому, что вероятность попадания отказа в вентили, принадлежащие регистру команды, должна находиться на уровне 0,431.